DIVISION OF SPERRY RAND CORPORATION MILITARY OPERATIONS - UNIVAC PARK - ST. PAUL, MINN. The UNIVAC 1206 Military Real Time Computer and the AN/USQ-20 NTDS Unit Computer are terms that have been used interchangeably.

The designation UNIVAC 1206 has been used by Remington Rand UNIVAC to indicate uses of the computer outside of the Naval Tactical Data System. The actual Military designation of this computer is CP 642A/USQ-20(V) indicating that it is one of a number of components included under the designation AN/USQ-20(V); others include such items as the power supply. USQ-20 is a general term used informally to identify this computer.

The technical specifications included in this report are applicable identically with this computer whether it is called UNIVAC 1206, CP 642A/USQ-20(V), or, loosely, USQ-20. The content of these specifications is nearly identical to that of the original technical Note No. 244, dated 10 October, 1960, titled AN/USQ-20 Unit Computer Characteristics.

# UNIVAC 1206 MILITARY COMPUTER

### GENERAL DESCRIPTION AND INPUT/OUTPUT SPECIFICATIONS

# 1206

# CONTENTS

### Page

| INTRODUCTION                  |   | • | • | • | • |   |   | • | 1  |

|-------------------------------|---|---|---|---|---|---|---|---|----|

| GENERAL COMPUTER ORGANIZATION | • |   | • |   |   |   |   | • | 2  |

| OPERATION                     |   | • | • |   |   |   |   |   | 5  |

| CONSOLE CONTROL               |   |   |   |   |   |   |   | • | 8  |

| OTHER FEATURES                |   | • |   |   | • |   | • | • | 10 |

| INPUT-OUTPUT SPECIFICATIONS   |   | • |   |   | • | • | • | • | 13 |

| PERIPHERAL EQUIPMENT          |   | • | • |   |   |   | • | • | 18 |

| INSTALLATION REQUIREMENTS     |   | • | • |   |   |   |   | • | 24 |

### APPENDIX A-REPERTOIRE OF INSTRUCTIONS

### AND PROGRAM TIMING

| INTRODUCTION              | A-1  |

|---------------------------|------|

| LIST OF INSTRUCTIONS      | A-7  |

| TYPICAL INSTRUCTION WORDS | A-19 |

### UNIVAC 1206 SPECIFICATIONS

HEIGHT-72.0 inches-182.8 centimeters. DEPTH-36.9 inches-93.7 centimeters. WIDTH-38.1 inches-96.8 centimeters. WEIGHT-2320 pounds-1052 kilograms.

# ILLUSTRATIONS

,

F

•

| Figure No. |                                           | P | age |

|------------|-------------------------------------------|---|-----|

| 1          | UNIVAC 1206 Military Computer             |   | 3   |

| 2          | Computer Cabinet Interior                 |   | 3   |

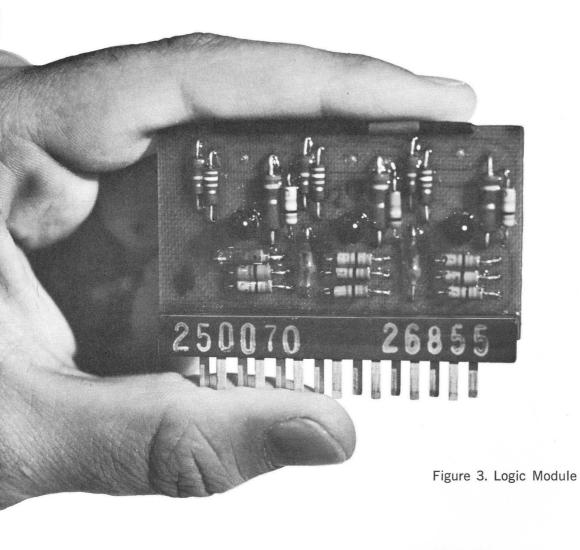

| 3          | Logic Module                              |   | 4   |

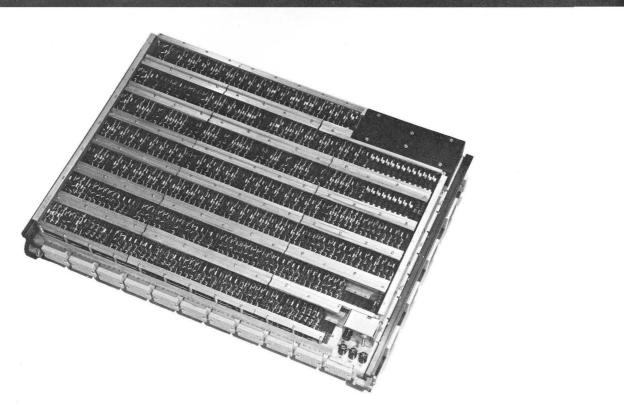

| 4          | Tray Assembly                             |   | 4   |

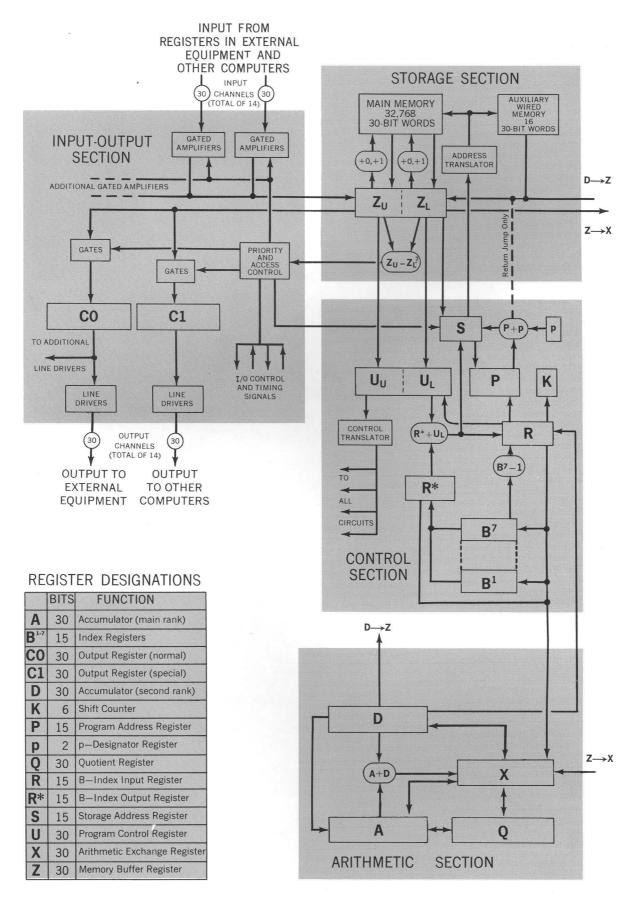

| 5          | UNIVAC 1206—Simplified Block Diagram      |   | 6   |

| 6          | Maintenance and Control Panel             |   | 9   |

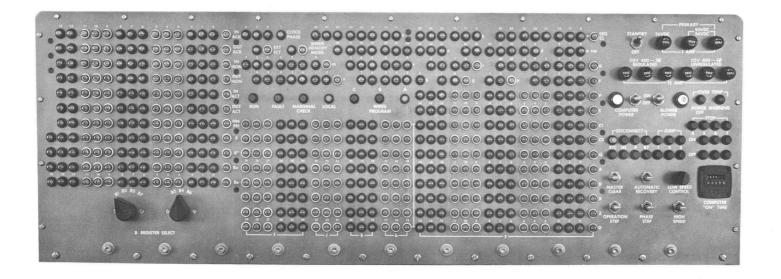

| 7          | Operating Console                         |   | 9   |

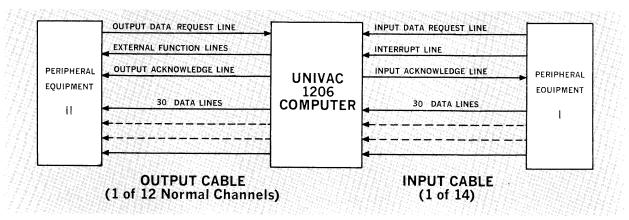

| 8          | Input-Output Cable Connections            |   | 13  |

| 9          | Connections from Computer A to Computer B |   | 15  |

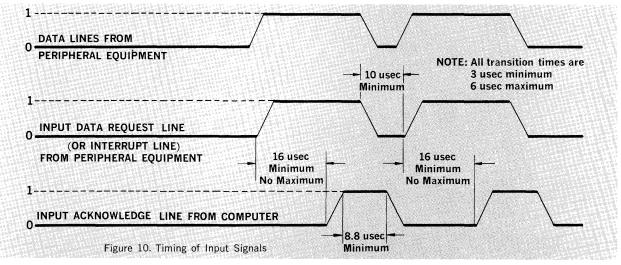

| 10         | Timing for Input Signals                  |   | 16  |

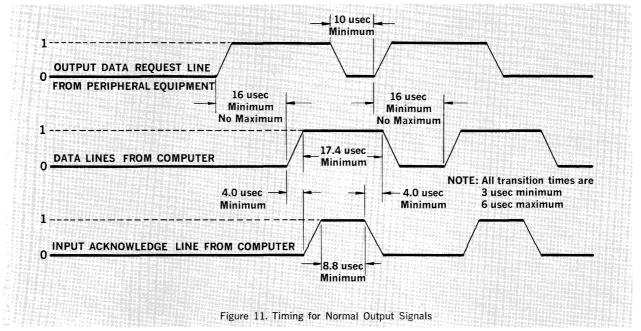

| 11         | Timing for Normal Output Signals.         |   | 17  |

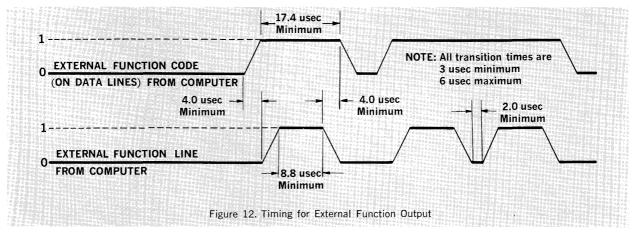

| 12         | Timing for External Function Output       |   | 17  |

### TABLES

| Table No. |                                                              | Page  |

|-----------|--------------------------------------------------------------|-------|

| 1         | Summary of Equipment Physical Characteristics                | . 23  |

| A-1       | UNIVAC 1206—Repertoire of Instructions                       | . A-2 |

| A-2       | UNIVAC 1206—Interpretation of Instruction Word Designators . | . A-3 |

| A-3       | UNIVAC 1206—Core Memory Address Assignments                  | . A-6 |

| A-4       | CS-1 Compiler—Phase Three                                    | A-18  |

### INTRODUCTION

The UNIVAC 1206 Military Computer is a general-purpose stored-program machine capable of processing very rapidly a large quantity of complex data. Major features of the UNIVAC 1206 Military Computer include the following:

- 1) Internal high-speed storage with a cycle time of 8 microseconds and a capacity of 32,768 words (16,384 optional);

- 2) Repertoire of 62 instructions, most of which provide for conditional program branches;

- 3) 30-bit word length;

- 4) Optional operation with 15-bit half-words;

- 5) Internally stored program;

- 6) Programmed checking of data parity;

- 7) Parallel, ones' complement, subtractive arithmetic;

- 8) Single-address instructions with provision for address modification via seven index registers;

- 9) Internal 7-day real-time clock for initiating operations at desired times;

- 10) 12 input and 12 output channels for rapid data exchanges with external equipment without program attention;

- 11) 2 input and 2 output channels for intercomputer data transfer;

- 12) 16-word wired auxiliary memory, for storage of critical instructions and constants, which provides facility for Automatic Recovery in event of program failure and for automatic initial loading of programs.

The following specifications were used as the basis for the design and construction of the UNIVAC 1206. . . . . . . . . . . . . General Electronic Equipment MIL-E-16400 . . . . . . . . . (Reliability, Simplicity, Materials, Workmanship, Production and Control Inspection, Ease of Operation and Maintenance) Enclosure Technical Manuals Drawings

### **GENERAL COMPUTER ORGANIZATION**

The UNIVAC 1206 Military Computer is a stored-program computer intended for rapid handling of large quantities of complex data. The computer is especially suitable for real time applications such as missile guidance, range safety, process monitoring, and tactical control and display. Relative to other general-purpose systems, the UNIVAC 1206 Computer emphasizes rapid communication with external devices and large, randomly accessible, internal storage.

Single-address instructions are employed and have an average execution time of 16 microseconds. Instruction words are 30 bits; data words can be either 15 or 30 bits.

Internal storage of the UNIVAC 1206 Military Computer consists of a 32,768-word ferrite core memory. Each word may be interpreted as a single 30-bit word, or as two 15-bit words individually addressed. Control, Arithmetic, and Input-Output sections of the computer each have access to the Storage section. A complete cycle for storage of a 30-bit word received from one of the other sections requires eight microseconds.

Arithmetic and logical operations are performed in the parallel binary mode. In most instances, the result of an operation appears in a 30-bit accumulator register. Arithmetic is ones' complement sub-tractive with a modulus  $(2^{30}-1)$ .

Computer operation is controlled by a stored program capable of self-modification. Each program instruction contains a function code (6 bits), instruction operand designator (15 bits), and three execution modifiers (3 bits each). Execution modifiers provide for address incrementation, operand interpretation, and branch-point designation. The operand may be increased by the amount contained in any one of seven index registers. The operand specified by the execution address may be interpreted as a 30-bit quantity, or as a 15-bit half-word with or without sign extension. The next sequential program step may be skipped; it is under control of the content of the Accumulator or the Q-register.

Communication between UNIVAC 1206 Military Computer and its associated external equipment is normally handled by a block transfer of data, with timing under control of the external device. Operating asynchronously with the main computer program, such transfers of data have independent access to storage.

A communication path is established by a sequence of request and response signals between external equipment and computer. Such signals may originate in either the computer or the external device. The main computer program is interrupted by external request signals and a communications channel is established. Once the link has been created, the computer returns to the main program sequence. Block transfer of input or output data then proceeds without program reference until completed.

A total of 14 input and 14 output channels is provided in the computer; each channel consists of 30 parallel lines. Two input and two output (special) channels are reserved for communication with other computers. The maximum possible transfer rate of input or output data over a given channel is greater than 30,000 words per second.

Output channels carry *External Function Words* as well as data words to external equipment. These specify the function desired of the external device. An External Function Word to a tape control unit, for example, may specify *Rewind Tape Unit 2*.

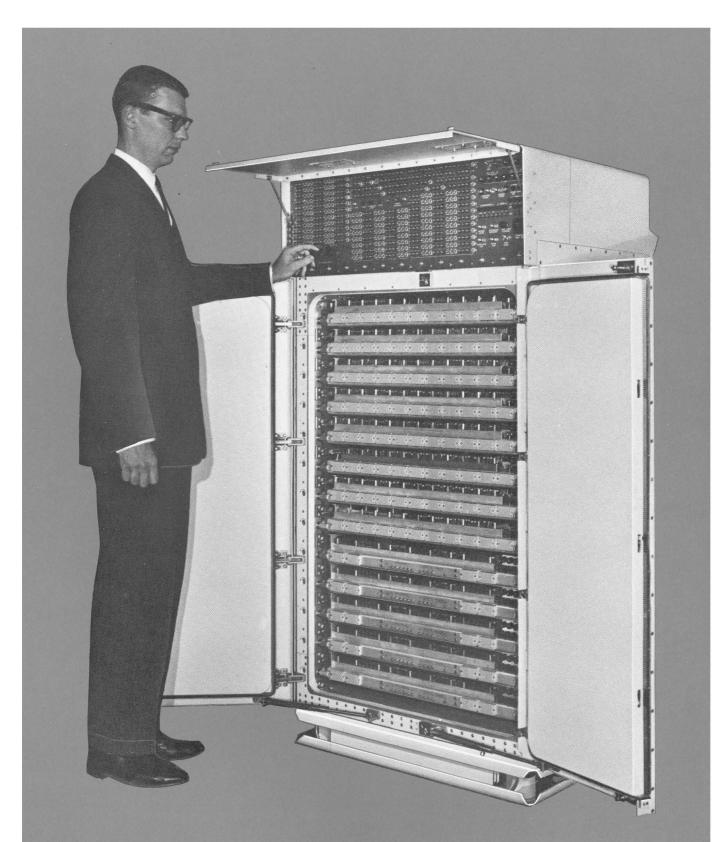

Figure 1. UNIVAC 1206 Military Computer

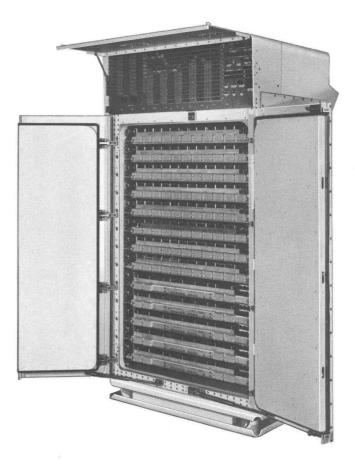

Figure 2. Computer Cabinet Interior

The computer (Figure 1) is housed in a single cabinet, 37 inches deep, 38 inches wide, and 72 inches high. Thirteen trays, eight of logic and five of memory, are horizontally arrayed within the cabinet (Figure 2). Logic modules (Figure 3) are encapsulated printed-circuit cards which plug into the trays (Figure 4). Maintenance test points are readily accessible at the front of the trays.

Computer cabinet doors, closed during normal operation, can be opened for maintenance. The maintenance and control panel, which forms the upper part of the cabinet, contains register indicators, set and clear pushbuttons, and operating switches. A separate operating and maintenance console can be supplied for applications where a remote console is desirable.

Primary power is provided to the computer from a 60-cycle input, 400-cycle output motor-alternator which, in addition to converting frequency, serves to isolate the computer from the main power source. The standard UNIVAC 1206 is equipped with a water-cooled heat exchanger. A plenum which uses ambient air as a coolant is available as an option. Inter-equipment cabling enters the computer at the top of the cabinet and may be run either overhead or through floor ducts.

The computer is designed and constructed to withstand severe shock and vibration. It may be installed aboard ship or in a trailer without modification.

Figure 4. Tray Assembly

# OPERATION

Figure 5 is a simplified block diagram of the UNIVAC 1206 Military Computer. As indicated, the computer consists of four major sections: Input-output, Storage, Arithmetic, and Control. Symbols on the diagram are explained as operation of the various sections is discussed.

### INPUT-OUTPUT SECTION

The *Input-output section* includes those data paths and control circuits used by the computer for communicating with external equipment. Main parts of the Input-Output section are 1) two output registers (C0 and C1) and their associated line drivers, 2) fourteen sets of gated input amplifiers, and 3) priority and access control circuits.

### Output Registers

The *Co-register* is used for transmissions to all external devices except other computers. As illustrated in Figure 5, C0 receives its input directly from the Storage section via gates controlled by the priority and access circuits. Three sets of 30 line drivers branch from the output of C0; each set drives four output channels. Gated registers located in the external devices determine which channel is active during any particular transmission.

The C1-register handles transmissions over the two special output channels—those used to transmit data to other computers. Operation of C1 is similar to that of C0: Words enter C1 from storage via gates controlled by the priority and access circuits and are transmitted over the active channel by a set of 30 line drivers.

The fourteen output channels are numbered from 0 to  $15_8$ ; the intercomputer channels are 0 and 1. If two or more output transmissions are simultaneously requested, the channel with the highest number is granted priority; others follow in order.

### Input Amplifiers

A set of 30 gated amplifiers is provided for each of the fourteen input channels. Gates are controlled by the priority and access circuits, with the channel having the highest number being given priority if two or more inputs are simultaneously requested. As in the case of the output channels, Channels 0 and 1 are used for intercomputer communication.

This method of treating input data eliminates the need for input buffer registers and gives external equipment direct access to the computer's internal memory.

### Priority and Access Control

The Priority and Access Control circuitry implements the assignment of access to the core memory. In the event of two or more simultaneous requests for access to memory, the priority and access circuitry evaluates the nature of the requests and assigns priority on the basis of the following established sequence.

- 1. Advance Real Time Clock.

- 2. External Interrupt.

- 3. Internal Output Monitor Interrupt.

- 4. Internal Input Monitor Interrupt.

- 5. Output Request on a normal channel.

- 6. Input Request.

- 7. Output Request on an intercomputer channel.

If the same type of request occurs on two or more channels simultaneously, the priority and access circuitry assigns priority in descending order of channel numbers. For simultaneous requests on the intercomputer channels, priority assignment alternates between the two.

Figure 5. UNIVAC 1206 Simplified Block Diagram.

### STORAGE SECTION

The *Storage section* consists of main memory, wired auxiliary memory, and associated address, transfer, and control circuits.

The main memory, constructed of modular arrays of ferrite cores, has a capacity of 32,768 words of 30 bits each, is coincident-current driven, and is addressed via the address translator. Contents of the location specified by the address is read into the 30-bit Z-register. Because of optional use of 15-bit half-words, Z is split into two 15-bit sections termed Z-upper ( $Z_U$ ) and Z-lower ( $Z_L$ ).

The memory operates in the destructive read-out mode. Time required for the read/restore cycle is eight microseconds.

During the restore portion of the cycle, the contents of  $Z_L$  or  $Z_U$  may be increased by one, as indicated by the +0, +1 modifier boxes. This provision allows for automatically increasing the I/O control words, with the result that memory locations interrogated during a block transfer of data are automatically advanced.

The comparator,  $Z_U = Z_L$ ?, is used to detect coincidence between the two halves of the I/O control word. When coincidence occurs, a signal is generated to terminate the I/O transfer.

### ARITHMETIC SECTION

The Arithmetic section is that part of the computer which performs numeric and logical calculations. Though greatly simplified, Figure 5 shows the important components of the Arithmetic section: the A-, D-, Q-, and X-registers and the add network.

The A-register (30 bits) may be thought of for programming purposes as a conventional accumulator. Because of the logic employed, however, the A-register is actually only the main rank of the accumulator; the *D-register* serves as a second rank. This configuration, while different from former and usual arrangements, permits the use of a much more reliable building-block circuit.

The Add operation is typical of the relationship between the A- and D-registers: The augend and addend are initially contained in A and D. As addition is performed, the sum is formed in parallel by the add network and placed in the *X*-register. From X, the sum is transmitted to A.

The Q-register (30 bits) is used principally during multiply and divide operations. The contents of both A and Q may be shifted left or right, individually or as one double-length 60-bit word.

### CONTROL SECTION

The *Control section* consists of those registers and circuits necessary to procure, modify, and execute instructions of the program.

The U-register (30 bits) is the program-control register. It holds the instruction word during execution of an instruction. The function code and the various execution modifiers are translated from appropriate sections of the register. The lower-order 15 bits of the U-register have addition properties, modulus  $2^{15}-1$ .

The 15-bit *B*-registers,  $B^1$  thru  $B^7$ , store the quantities used for address modification. In addition,  $B^7$  stores the count for the repeat mode of operation.

The *R*-register (15 bits) functions as input register for the B-registers. It also has counting properties to increase the contents of the B-registers. The R\*-register is the B-index output register, it holds the quantity added to the lower-order 15 bits of the U-register during address modification.

The K-register (6 bits) functions as a shift counter for all arithmetic operations that involve shifts. The maximum shift count is 63 octal. Multiply and divide operations are controlled by pre-setting the K-register to ZERO and counting operational steps.

The *S*-register (15 bits) holds the storage address during memory references. At the beginning of a storage access period, the address is transferred to the S-register. The contents of the S-register are then translated to activate the storage selection system.

The *P*-register (15 bits) holds the memory address of a computer instruction word—that of the current instruction or of a new instruction (e.g., as a result of a jump condition).

The *p*-register (2 bits) adds an increment of +0, +1, or +2 to the contents of the P-register. Output of the adder is the memory address of the *next* instruction and is transferred to the S-register. In the case of a Return Jump instruction *only*, output of the adder is transferred to the Z-register and stored in memory.

## **CONSOLE CONTROL**

Both the self-contained maintenance and control panel (Figure 6) and the separate (optional) operating console (Figure 7) include indicator lamps that display a detailed report of the internal status of the computer, and controls that allow varied manually governed operations. It is not necessary to monitor the consoles during normal operation.

#### REGISTERS

Each register is represented on a console by a row of display lamps, each of which indicates the content of a corresponding register bit-position; a row of SET buttons, each of which can be used to manually enter a *one* into the corresponding bit-position; and a CLEAR button, which can be used to enter zeros manually into all bit-positions of the register. Many of the registers are involved in the mechanics of executing instructions, and are not directly accessible to the program. (These registers are not discussed in this publication.)

#### SPECIAL MODES

Both the maintenance and control panel and the separate console are provided with manual controls that permit the following special modes of operation:

- 1) Execution of one program instruction of a sequence for each depression of a switch.

- 2) Execution of consecutive program instructions at a low rate governed by a console frequency control.

- 3) Execution of one master clock phase for each depression of a switch.

- 4) Execution of consecutive master clock phases at a low rate governed by a console frequency control.

- 5) Operation that is normal except that the computer does not stop when it executes a programmed *Stop* instruction. (Such operation is called abnormal high-speed operation.)

The consoles are also provided with a manual control that may be used to disable the real-time clock. This option enables the operator to suspend normal operation temporarily without affecting such operation when it is subsequently resumed. Such suspensions could include stopping the computer or operating temporarily in one of the special modes listed previously.

Figure 6. Maintenance and Control Panel

Figure 7. Operating Console

### **OTHER FEATURES**

The UNIVAC 1206 Military Computer can be used in a wide range of applications, including scientific problems that have previously been limited to very large general-purpose computers and other problems that have ordinarily been solved by business machines. It is especially well suited to real-time control, data processing, and data reduction. Most of the basic features of the computer are described in previous sections. A detailed account of how these features may be used is beyond the scope of this document. This section, however, suggests uses of certain computer features in a few areas.

Features considered here are: 1) automatic programming, 2) floating-point arithmetic, 3) the real-time clock, 4) masked comparison, 5) inclusion of operands in instruction words, 6) detection of special faults, 7) program branching, 8) search operations, 9) half-word and full-word logic, 10) external and internal program interrupts, and 11) 16-word wired auxiliary memory.

### AUTOMATIC PROGRAMMING

Automatic Programming for the UNIVAC 1206 computer is in the form of an extensive program processing system that produces, from information coded in an English-algebraic shorthand, a running program complete with memory allocation. There is provision for the detection and correction of errors, editing the program, and debugging the program once it has been placed in operation. There are two distinct coding levels: the AS-1 assembly language, which is computer oriented, and the CS-1 compiling language, which is problem oriented as well as computer oriented. In addition, CS-1 includes an extensive magnetic tape subroutine library.

Programs prepared using AS-1 closely parallel machine coded programs, however, they are readable without reference to charts or tables. As a further advantage, AS-1 language can specify, by a single code, certain operations that require several machine instructions. Coding in AS-1, of course, requires a thorough knowledge of UNIVAC 1206 operation. The system requires 32K core memory and peripheral equipment consisting of a paper tape reader and punch unit and an on-line typewriter or teletypewriter unit.

The CS-1 compiling system includes all the features of AS-1 but has a far broader scope. CS-1 is not limited to machine oriented language, nor does its use require extensive knowledge of computer operation. CS-1 features a number of very powerful *operators* that are totally divorced from machine code. Table A-4 lists the CS-1 operators and indicates the CS-1 programming format. From its extensive *dual* magnetic tape subroutine library, CS-1 has access to numerous computational and manipulative processes. One library portion, called Compiler Library, contains a fixed set of subroutines that control various peripheral equipments when incorporated in the generated program. Such equipment control includes the monitoring typewriter paper tape punch, and the high-speed printer. The other library portion stores subroutines selected by individual programming groups for convenient retrieval. These generally consist of computational routines. Computational routines currently available include square

root, sine, cosine, tangent, arcsine, and arccosine. Routines are also available for coordinate conversion and for conversion from octal-to-decimal and decimal-to-octal notation.

The CS-1 compiling system operates in core memory with three magnetic tape units for additional storage, and one for a User Library. The compiler produces a variety of listings on a high-speed printer such as: side-by-side (input vs. machine code output) listings, sorted allocations, corrected programs, etc.

Input coding is presented to CS-1 either on 80-column cards or on paper tape. Compiled object programs may be placed either on paper tape or magnetic tape.

### FLOATING-POINT ARITHMETIC PROGRAM PACKAGE

The floating-point format is based on a two-word information unit: one mantissa word and one characteristic word. The length of the mantissa word is 28 bits; the length of the characteristic word is 15 bits, including sign bit. It is a three-address system in which four B registers are used to designate operand and operation code. The average instruction time for a floating-point operation (*add, subtract, multiply*, or *divide*) is 500 microseconds.

### REAL-TIME 7-DAY CLOCK

Among the features that suit the computer to real-time problems is the 7-day clock which contains an accurate record of time. The clock may be used to log the receipt times of a periodic real-time input. Each message may be recorded together with its receipt time. Another use of the clock is to initiate periodic programmed operations without requiring more than occasional attention of the main program. Since the clock recycles only once in 7 days, it is suitable for use where the computer is used on an around-the-clock basis.

### MASKED COMPARISON

Masked Comparison is used to compare all or any part of a word with the contents of the accumulator. It also tests for *equality*, and *non-equality*, *greater than*, or *less than* conditions. In all cases, the original content of the Accumulator is left unchanged.

### INCLUSION OF OPERANDS IN INSTRUCTION WORDS

The lower half (15 bits) of an instruction word is commonly used as an operand address. Where 15-bit operands provide acceptable precision, the lower half of the instruction word itself may serve as an operand. This option of storing the operand as part of the instruction word is particularly advantageous for certain applications. It reduces computation by eliminating a memory reference and doubles storage potential.

### DETECTION OF SPECIAL FAULTS

Various *fault* conditions can arise during the operation of a running program. For example, an attempt to execute an illegal function code (i.e., 00 or 77) constitutes a fault. Two fault conditions can arise in the execution of a *divide* instruction: the division may be zero or the quotient may exceed 30 bits in length. In each case, the computer can automatically detect the fault and take appropriate remedial action.

### PROGRAM BRANCHING

The instruction repertoire of the computer includes provision for program branching that is economical both of memory capacity and instruction execution time. By means of designator bits in the instruction word, it is possible to include in any instruction in a running program, provision for altering the established sequence of instructions without an additional memory reference.

Most instructions can include provision for skipping the next instruction in the regular sequence upon

the occurrence of some specified condition. Other instructions make possible the conditional execution of the instruction at a specified storage location—with or without automatic return to the branch point. Still another type of instruction can establish various iterations of a given instruction. By proper combination of instructions, of course, it is possible to set up numerous compound branch conditions.

### SEARCH OPERATIONS

The computer can search internally stored files at very high speeds. The search identifier is entered into the Accumulator, and a mask that identifies the key (a *one* at every key bit position) is entered in Q. The search consists of a masked comparison that is performed repeatedly at successive memory addresses until a *find* (or other terminal condition) is detected.

### HALF-WORD AND FULL-WORD LOGIC

All instructions that procure their operands from memory may select the upper 15 bits, the lower 15 bits, or the entire 30 bits as the operand. For some purposes, half-word accuracy is generally sufficient, and this feature can be used to reduce computation time and to double the effective memory capacity.

### EXTERNAL AND INTERNAL PROGRAM INTERRUPTS

Provision is made for the interruption of a running program by an event which may occur asynchronously with that program.

Any interrupt discontinues the normal execution of instructions by forcing the execution of the instruction located in a permanently assigned "Interrupt Entrance Register". For each of the 14 input-output channels there are three Interrupt Entrance Registers.

- External Interrupt Register

- Internal Interrupt Register for Input

- Internal Interrupt Register for Output

Conventionally, all interrupt locations are filled with one of two types of instructions:

- To ignore the interrupt, a 60000 00000 instruction will remove the interrupt lockout; and the program will continue with the normal execution of instructions, since the P-register is not affected by the interrupt itself.

- To respond to the interrupt requires a Return Jump to the interrupt routine in the interrupt entrance register. The Return Jump instruction saves the contents of the P-register plus one, which is the address of next instruction that would have been executed in the normal sequence if no interrupt had occurred, rather than the address of the Return Jump instruction + 1. This provides a return to the program that was interrupted at the point of interruption.

An external interrupt results from an external device placing a signal on an External Interrupt line. Appropriate action is generally taken by an interrupt program.

Internal interrupts are generated by the input-output section of the computer whenever a buffer, which has been initiated with a monitor imposed, terminates at the end of the transfer. The interrupt program takes cognizance of the buffer termination, and the main program is resumed.

A fault interrupt is a special case of internal interrupt caused by executing an illegal function code, i.e., 00 or 77.

### 16-WORD WIRED AUXILIARY MEMORY

In addition to the large main memory, a 16-word auxiliary memory is also provided. It is a wired memory and operates in the nondestructive read-out mode. The auxiliary memory is used to contain important instructions or constants. For example, a program-load routine may be stored there to facilitate rapid changes in the main program and automatic program recovery.

## INPUT-OUTPUT SPECIFICATIONS

#### GENERAL

Communication with the UNIVAC 1206 Military Computer is carried on in a 30-bit parallel mode. The computer is provided with 14 input channels, and 14 output channels. The output channels are divided into 12 normal and 2 special output channels. External Function Codes are carried over the same 30 lines as are used for output data, but the control signals used with External Function Codes are carried on different lines to indicate the nature of the signals on the 30 lines. The two *special* output channels differ from the normal channels only in timing and control of data transfer. All input-output channels maintain the same electrical specifications.

Note that all references to input or output are made from the standpoint of the computer; that is, *input* is input to the computer and *output* is output from the computer.

#### CONTROL COMMUNICATION

The UNIVAC 1206 Military Computer is designed to use a d-c level input-output system. Signals are d-c levels which may be changed upon interchange of control information. Signals may exist for microseconds or days, depending on the nature of the particular task.

It should be noted that the control lines are carried in the same cables as the data lines and have the same voltage levels. Hence, delay times, rise and fall times, and storage times are similar.

### DATA AND CONTROL SIGNALS

Each input and each output channel has its own cable associated with it (28 cables in all). Each cable has 30 data lines plus 3 control lines.

Figure 8 shows the UNIVAC 1206 Military Computer receiving input from Equipment I and sending output to Equipment II. Of course in most cases, both input and output cables will be used on the same peripheral equipment. Only normal output channels are used for output to peripheral equipment. Any

Figure 8. Input-Output Connections

input channel may be used for input from peripheral equipment. Notice the direction of information flow. "Request" and "Interrupt" signals always originate at the peripheral equipment. "Acknowledge" and "External Function" signals always originate at the computer. The Acknowledge signals are always sent from the computer to the peripheral equipment. The third set of control signals, called Interrupt in the input cable and External Function in the output cable is always sent in the same direction as data flow.

### SEQUENCE OF EVENTS

The sequence of events for each of four cases of communication between the UNIVAC 1206 Military Computer and peripheral equipment follows:

Normal Input Data Transfer to Computer from Equipment I (Buffer mode).

- 1) Computer initiates input buffer for given channel.

- 2) Peripheral equipment places data word on 30 data lines.

- 3) Peripheral equipment sets the Input Data Request line to indicate that it has data ready for transmission.

- 4) Computer detects the Input Data Request.

- 5) Computer samples the 30 data lines at its own convenience.

- 6) Computer sets the Input Acknowledge line, indicating that it has sampled the data.

- 7) Peripheral equipment senses the Input Acknowledge line.

- 8) Peripheral equipment drops the data lines and the Input Data Request line.

Steps 2) through 8) of this sequence are repeated for every data word until the number of words specified in the input buffer has been transferred.

#### Transmission of an Interrupt Code to Computer from Equipment I

- 1) Peripheral equipment places the Interrupt code on the 30 data lines.

- 2) Peripheral equipment sets the Interrupt line.

- 3) Computer detects the Interrupt.

- 4) Computer samples the 30 data lines.

- 5) Computer sets the Input Acknowledge line, indicating that it has sampled the data.

- 6) Peripheral equipment senses the Input Acknowledge line.

- 7) Peripheral equipment drops the Interrupt code from the data lines and the Interrupt line.

Note that the *Input Acknowledge* is the computer response to either an *Input Data Request* or to an *Interrupt*. To eliminate misinterpretation of the *Input Acknowledge* signal, peripheral equipment must not interrupt until its last *Input Data Request* has been acknowledged by the computer. Under emergency conditions, when data loss is of secondary importance, the *Input Data Request* may be dropped and the *Interrupt* raised a minimum of 100 microseconds later.

When these conditions prevail, an *Input Acknowledge* that occurs after the *Interrupt* is raised will be in answer to the *Interrupt*.

#### Normal Output Data Transfer from Computer to Equipment II (Buffer Mode).

- 1) Computer initiates output buffer for given channel.

- 2) Peripheral equipment sets the Output Data Request line indicating that it is in a condition to accept data.

- 3) Computer detects Output Data Request.

- 4) Computer (at its convenience) places information on the 30 data lines.

- 5) Computer sets the Output Acknowledge line, indicating that data are ready for sampling.

- 6) Peripheral equipment detects the Output Acknowledge.

- 7) Peripheral equipment may drop Output Data Request anytime after detecting Output Acknowledge.

- 8) Peripheral equipment samples the 30 data lines.

- 9) Computer drops Output Acknowledge and data lines.

Steps 2) through 9) of this sequence are repeated for every data word until the number of words specified in the output buffer have been transferred.

Transmission of an External Function Code from Computer to Equipment II.

- 1) Computer places the External Function Code on the 30 data lines.

- 2) Computer sets the External Function line.

- 3) Peripheral equipment detects the External Function line.

- 4) Peripheral equipment samples the 30 data lines.

- 5) Computer drops External Function Code on the 30 data lines and the External Function line.

### USE OF SPECIAL OUTPUT CHANNELS

Communication between two computers requires using the two special output channels. Figure 9 illustrates the connections for Computer A to transmit data to Computer B. Another cable using a special output channel of Computer B and an input channel of Computer A would be necessary if Computer B were going to transmit data to Computer A.

|                        |        | INPUT BUFFER ACTIVE |                       |

|------------------------|--------|---------------------|-----------------------|

|                        | READY  | INPUT DATA REQUEST  |                       |

| COMPUTER               | RESUME | INPUT ACKNOWLEDGE   | COMPUTER              |

| A<br>SPECIAL<br>OUTPUT | 30 DAT | A LINES             | B<br>INPUT<br>CHANNEL |

| CHANNEL                |        |                     | CHANNEL               |

|                        |        |                     |                       |

Figure 9. Connections from Computer A to Computer B

Normal transfer of data from computer A to Computer B (Buffer Mode) takes place as follows:

- 1) Computer B sets Input Buffer Active signal.

- 2) Computer A detects Input Buffer Active signal.

- 3) Computer A places data on 30 data lines.

- 4) Computer A sets Ready which becomes Input Data Request in Computer B.

- 5) Computer B detects Input Data Request.

- 6) Computer B samples 30 data lines.

- 7) Computer B sets Input Acknowledge line (returned to Computer A as Resume).

- 8) Computer A senses *Resume* line.

- 9) Computer A drops data lines and Ready line.

Steps 3) through 9) of this sequence are repeated for every data word. Input Buffer Active remains energized during entire transfer of block of words.

#### TIMING

Data lines, when transmitting data from computer to equipment, *must be stable* before being sampled. Hence, a 4.4-microsecond fixed time delay exists between the computer's loading of an output register and energizing of the Output Acknowledge signal or of the External Function signal.

#### Input Timing Considerations

The Input Data Request signal indicates to the computer that data have been placed on the 30 input data lines. To ensure that the data will be accepted, the Input Data Request (or Interrupt) must be

maintained on the lines until an answering Input Acknowledge is received. As shown in Figure 10, there is a 16-microsecond minimum delay between the setting of the Input Data Request and its answering Input Acknowledge. There is no maximum limit stated for the delay, since its value for any particular cycle is determined by the interaction with the computer program and the other input-output channels. The data lines must remain stable as long as the Input Data Request is up.

The Input Acknowledge indicates to peripheral equipment that its 30 data lines have been sampled. The Input Acknowledge signal is set for a fixed time interval. The Peripheral Equipment must be capable of detecting as an Input Acknowledge, a signal which may exist in the stable *one* state for as little as 8.8 microseconds. The Input Data Request (or Interrupt) line and data lines may be dropped to the *zero* state anytime after detecting the Input Acknowledge. The Input Data Request cannot be reset immediately to indicate readiness of a second data word because the computer will not recognize the second Input Data Request unless a minimum time delay of 10 microseconds is allowed between the start of the dropping of the first Input Data Request and the start of the setting of the second Input Data Request. Figure 10 shows that the timing would allow peripheral equipment wishing to transmit data to the computer at a maximum rate to legitimately set the Input Data Request to the *one* state for the second time before the first Input Acknowledge had dropped to the *zero* state. However, this will not affect operation of the cycle since a 16-microsecond minimum delay will again be required between the setting of the second Input Data Request and the setting of the second Imput Acknowledge.

### Output Timing Considerations (Buffer Output)

Peripheral equipment must first set the Output Data Request line, indicating that it is in a condition to accept a word of data from the computer. This is necessary because data will be available to the peripheral equipment in a stable state for an interval which may be as short as 17.4 microseconds, if the computer is performing output operations at a maximum rate. Data lines will not necessarily be cleared to the *zero* state before being reset to the *one* state. The minimum time which may elapse between the request and the placement of answering data on the lines is 16 microseconds. The maximum time depends upon the computer program, the priority of the particular channel, and the data rates of the other peripheral equipment.

The Output Acknowledge signal indicates to the peripheral equipment that its requested data are now present on the data lines, which should now be sampled. As shown in Figure 11, the Output Acknowledge will be sent a minimum of 4.0 microseconds after the data has been placed on the lines. The peripheral equipment must be capable of recognizing, as an Output Acknowledge, a signal which may exist in the stable *one* state for as short a time as 8.8 microseconds. The computer will maintain stable data on the lines for a minimum of 4 microseconds after it starts to drop the Output Acknowledge. The Output Data Request may be dropped to the *zero* state anytime after detecting the Output Acknowledge. The Output Data Request cannot be reset immediately to indicate readiness of the

peripheral equipment to accept a second data word because the computer will not recognize the second Output Data Request unless a minimum time delay of 10 microseconds is allowed between the start of the dropping of the first Output Data Request and the start of the setting of the second Output Data Request. Figure 11 shows that the timing would allow peripheral equipment wishing to receive data from the computer at a maximum rate to legitimately set the Output Data Request to the *one* state for the second time before the first Output Acknowledge had dropped to the *zero* state. However, this will not affect operation of the cycle since a 16-microsecond minimum delay will again exist between the setting of the second Output Data Request and the availability of the second word on the data lines.

### Output Timing Considerations (External Function Output)

External Function output timing is unique in that no response is sent by the peripheral equipment. The computer places the External Function code on the 30 output data lines, and a minimum of 4.0 microseconds later energizes the External Function line. The External Function line indicates to the peripheral equipment that an External Function code is present on the data lines, which should now be sampled. The External Function line will remain in the stable one state for an interval which may be as short as 8.8 microseconds. The External Function code will remain on the data lines for a minimum of 4-microseconds after the External Function signal begins to drop.

The peripheral equipment has no control over the rate at which External Function codes are sent. If two External Function instructions to the same peripheral equipment are executed consecutively, the result will appear as in cycles 2 and 3 of Figure 12. The External Function line will drop to the zero state for an interval which may be as short as 2.0 microseconds. If the peripheral equipment cannot accept External Functions at this rate, restrictions must be made in the programming of External Function instructions to the equipment.

### PERIPHERAL EQUIPMENT

The following paragraphs contain brief functional descriptions of the various items of peripheral equipment available for use with the UNIVAC 1206 Military Computer. Table 1 summarizes the physical characteristics of the computer as well as the peripheral equipment.

PAPER TAPE UNIT Inches: Height 54.7, Width 22.0, Depth 22.5 Centimeters: Height 141.5, Width 55.8, Depth 57.2

The Paper Tape Unit contains within a single enclosure a photoelectric reader, a high-speed punch and the necessary buffering and control circuits to match the interface of the UNIVAC 1206 Computer. The reader operates at 200 frames per second, the punch at 60 frames per second. The unit provides the capability of retrieving anything stored in the computer memory in a form that facilitates manual checking, modification, and subsequent re-entry into the system.

TELETYPE\* MODEL ASR-28 AND ADAPTER Inches: Height 40.5, Width 46.0, Depth 26.5 Centimeters: Height 103.0, Width 116.5, Depth 67.3

Teletype\* Model ASR-28, Automatic Send-Receive set, is a code-actuated page printer and 5-level paper tape punch and reader with keyboard input. It is capable of operating at rates of 60, 75, and 100 words (5 characters plus a space) per minute. It can prepare printed copy from keyboard input, remotely generated signals, or 5-level paper tape. It can produce 5-level punched paper tape from keyboard input, remotely generated signals, or from another 5-level tape. It can produce output signals for transmission either from keyboard input or 5-level tape. It can produce printed copy, punched paper tape, and remote output signals concurrently.

Via the Teletype Adapter, the Teletype provides one medium for data entry into, and retrieval from the UNIVAC 1206 computer. The Teletype Adapter contains the logic necessary to match the interfaces of the two pieces of equipment; Teletype signals are serial (one character at a time), whereas the computer transfers data in the parallel mode.

\*Teletype is a trade mark of the Teletype Corporation.

### MONITORING TYPEWRITER Inches: Height 48.0, Width 27.3, Depth 25.0

Centimeters: Height 122.0, Width 69.2, Depth 63.5

The Monitoring typewriter for use with the UNIVAC 1206 Military Computer is the Flexowriter<sup>\*</sup>, model FL. Upon appropriate commands from the computer, it can prepare printed copy of any information stored in the computer. Operating independently of the computer, it can prepare simultaneously (if desired) printed copy and seven-level punched paper tape either from keyboard entry or from a compatible paper tape. The seven-level paper tape produced is compatible with the tape used by the 1206 punched paper tape unit. Thus, the Monitoring typewriter, in addition to its monitoring function, is a very useful tool for the preparation and editing of paper tapes.

MAGNETIC TAPE UNIT Inches: Height 72.0, Width 35.4, Depth 31.4 Centimeters: Height 183.0, Width 90.0, Depth.79.6

The Magnetic Tape Unit consists of two magnetic tape transports and associated control unit in a single cabinet. The control unit matches the interface of the UNIVAC 1206 computer. Data recording density is 200 seven-channel frames per inch on standard Mylar\*\* tape, 2400 feet long and one-half inch wide. Tape speed during read/write operation is 112.5 inches per second which yields a character transfer rate of 22.5 kc. The tape transports provide optical loadpoint and end-of-tape sensing.

The Magnetic Tape Unit provides a convenient means of transferring large amounts of stored data to and from the computer memory. The capacity of the unit is such that this can include program and parameter back-up. Data transfer to and from magnetic tape are asynchronous with respect to normal computer operation and is accomplished in the request/acknowledge mode.

MODULE TESTER

Inches: Height 37.3, Width 18.8, Depth 41.0 Centimeters: Height 93.3, Width 47.7, Depth 104.1

\*Flexowriter is a trade mark of Friden, Inc.

\*\*Mylar is a trade mark of the E. I. DuPont Nemours and Company, Inc.

The printed circuit module tester consists of a cabinet housing control panel, test circuits, power supplies, storage space for adapter plugs, and operation manuals. The module tester performs dynamic operational tests under simulated operating conditions. Approximately 140 adapter plugs, used to test the 1206 printed circuit modules, are furnished in addition to 14 blank adapter plugs. Necessary tools are also included for wiring the blank adapter plugs.

### KEYSET SYSTEM Inches: Height 72.0, Width 24.2, Depth 31.4 Centimeters: Height 183.0, Width 61.4, Depth 79.6

The Keyset System employs two types of equipment—Keysets and a Keyset Central. The Keyset is a general purpose manual digital data entry device. It includes a number of keys for the assembly of data entries, a readout device to monitor data entries during assembly, an Entry key to signal the presence of data to Keyset Central, a fault indicator, and a Clear key. It is readily adaptable to a variety of input functions by the use of appropriate keyboard overlays. Keyset Central is a scanning /switching device that can accept inputs from up to 48 Keysets. It matches the UNIVAC 1206 computer interface and provides error-detection capability in the form of automatic parity checking. Under computer control it sequentially scans all Keysets for the presence of data, transmits any such data to the computer, and clears the Keyset when the computer accepts the data.

Keyset Central can transfer data to the computer from digital sources other than Keysets. It can also transfer data from analog devices via 14 special analog-to-digital conversion channels. Any data entry requires preplanning so that the computer program will recognize and accept the entry as a valid input.

Unlike many forms of data entry, the Keyset System permits data transfer to the UNIVAC 1206 computer during an operational program without stopping the program. Typical functions that exploit this feature include:

- Enter and update data.

- Control the operation of communications links.

- Direct the computer to shift operational modes.

- Manually override normal computer decisions under abnormal conditions.

VIDEO PROCESSOR

Inches: Height 72.0, Width 35.3, Depth 31.8 Centimeters: Height 183.0, Width 89.5, Depth 80.6

The Video Processor accepts raw radar video and converts it to a form suitable for further processing by the UNIVAC 1206 computer. Under control of the system program it can discriminate against noise,

clutter, and other unwanted signals.

The Video Processors now in production at UNIVAC operate only with specific radar sets. Operation with other radars does not require extensive modification of present equipment.

### SYSTEM MONITORING PANEL Inches: Height 49.1, Width 13.0, Depth 38.8 Centimeters: Height 124.7, Width 33.0, Depth 98.3

The System Monitoring Panel provides manual computer control in a multi-computer complex. It enables an operator to control the entry of various selected programs and monitor intercomputer data transfer. It permits some degree of program error analysis by providing displays of certain pertinent information.

INTERCONNECTION PANEL Inches: Height 52.0, Width 31.0, Depth 15.0 Centimeters: Height 132.1, Width 78.7, Depth 38.1

The Interconnection Panel is a switchboard with ten multi-pole double throw switches. In a multicomputer equipment complex, it provides the capability of manually switching a piece of peripheral equipment from one computer to a second computer in the equipment complex. It can connect up to ten external devices to either of two computers. The Interconnection Panel greatly simplifies the task of altering the equipment configuration when necessary for maintenance, because of equipment failure, etc.

#### TERMINAL EQUIPMENT LOGIC

*Inches:* Height 72.0, Width 24.2, Depth 31.4 *Centimeters:* Height 183.0, Width 61.4, Depth 79.6

The interface between the 1206 computer and the communications terminal equipment is a unit called TEL (Terminal Equipment Logic). It can operate with either of two data links but not both simultaneously. Under computer control, it establishes and maintains net control and synchronization and accomplishes the automatic transmission of all data between sites. TEL also includes error detection and control-word recognition features.

NET PROGRAM DISPLAY Inches: Height 10.8, Width 13.0, Depth 14.4 Centimeters: Height 27.4, Width 33.0, Depth 36.5

The Net Program Display is a small alphanumeric display device that operates in conjunction with the Terminal Equipment Logic. Normally it displays the address of the station last called; if the called station misses its call, it displays the words MISSED CALL.

The UNIVAC 1206 can also use the following UNIVAC 490/1107 standard peripheral equipment: Model 46 High-Speed Printer (600 lines per minute) Model 45 Card Reader (600 cards per minute) Model 67 Card Punch (150 cards per minute) FH-880 Flying Head Magnetic Drum (approximately 4½ million characters) Uniservo IIA Magnetic Tape Subsystem

|                                                          |                                           |                                            | Di                     | MENSIC                 | INS                                       |                         | Ur<br>We                                        | ∛IT<br>IGHT         | Unit I<br>Requir<br>(Wa              | EMENTS                                   | Cooling<br>Require-<br>ments |

|----------------------------------------------------------|-------------------------------------------|--------------------------------------------|------------------------|------------------------|-------------------------------------------|-------------------------|-------------------------------------------------|---------------------|--------------------------------------|------------------------------------------|------------------------------|

| EQUIPMENT                                                |                                           | Inches                                     |                        | Ce                     | Centimeters                               |                         |                                                 | MS                  |                                      |                                          | Water**                      |

|                                                          | HEIGHT                                    | WIDTH                                      | DEPTH                  | HEIGHT                 | WIDTH                                     | DEPTH                   | POUNDS                                          | KILOGRAMS           | 115 volt<br>60 cycle<br>single phase | 115 volt<br>400 cycle<br>3-phase         | ot 65F                       |

| UNIVAC 1206<br>Military Computer<br>Motor-Generator      | 72.0                                      | 38.1                                       | 36.9                   | 182.8                  | 96.8                                      | 93.7                    | 2320                                            | 1052                |                                      | 2000*                                    | 6.3                          |

| Set*<br>MG Set Controller<br>Maintenance                 | 25.3<br>58.5                              | 31.4<br>19.5                               | 29.4<br>16.8           | 64.2<br>148.5          | $79.6 \\ 49.5$                            | 74.5<br>42.5            | $\begin{array}{c} 1000\\ 316 \end{array}$       | 454<br>144          |                                      |                                          |                              |

| Console                                                  | 48.0                                      | 51.0                                       | 31.5                   | 121.9                  | 129.5                                     | 80.0                    | 359                                             | 163                 |                                      | 100                                      |                              |

| Paper Tape Unit<br>Teletype & Adapter                    | $\begin{array}{c} 54.7\\ 40.5\end{array}$ | $\begin{array}{c} 22.0\\ 46.0 \end{array}$ | $22.5 \\ 26.5$         | $141.5 \\ 103.0$       | $55.8 \\ 116.5$                           | 57.2<br>67.3            | $\begin{array}{c} 260\\ 305 \end{array}$        | 118<br>139          | $500 \\ 200$                         | $\begin{array}{c} 200\\ 300 \end{array}$ |                              |

| Monitoring Type-<br>writer (Alternate)                   | 48.0                                      | 27.3                                       | 25.0                   | 122.0                  | 69.2                                      | 63.5                    | 300                                             | 137                 | 100                                  | 150                                      |                              |

| Magnetic Tape Unit<br>Module Tester<br>Keyset Central    | 72.0<br>37.3<br>72.0                      | 35.4<br>18.8<br>24.2                       | $31.4 \\ 41.0 \\ 31.4$ | 183.0<br>93.3<br>183.0 | 90.0<br>47.7<br>61.4                      | $79.6 \\ 104.1 \\ 79.6$ | $\begin{array}{c} 1400\\ 400\\ 960 \end{array}$ | $636 \\ 181 \\ 436$ | 2000                                 | $1400 \\ 120 \\ 1400$                    | 3.8<br>1.7                   |

| Keyset Universal<br>Video Processor<br>System Monitoring | 28.0<br>72.0                              | 12.7<br>35.3                               | 13.0<br>31.8           | 71.1<br>183.0          | 32,2<br>89,5                              | 33.0<br>80.6            | 95<br>1500                                      | 43<br>681           | 500                                  | 200<br>1600                              | 3.7                          |

| Panel                                                    | 49.1                                      | 13.0                                       | 38.8                   | 124.7                  | 33.0                                      | 98.3                    | 400                                             | 182                 |                                      | 240                                      |                              |

| Interconnection<br>Panel<br>Terminal Equipment           | 52.0                                      | 31.0                                       | 15.0                   | 132.1                  | 78.7                                      | 38.1                    | 250                                             | 114                 |                                      |                                          |                              |

| Logic<br>Net Program Display                             | 72.0<br>10.8                              | 24.2<br>13.0                               | 31.4<br>14.4           | 183.0<br>27.4          | $\begin{array}{c} 61.4\\ 33.0\end{array}$ | 79.6<br>36.5            | 995<br>50                                       | 452<br>23           |                                      | 1400<br>28                               | 1.7                          |

Table 1. Summary of Equipment Physical Characteristics

\*To isolate the computer from line transients, the MG set supplies 2500 watts of 115 volts, 400 cycle, 3-phase power to operate the computer—this does NOT include the 2000 watts required to operate the blowers. The MG set, as normally supplied, operates from 440 volts, 60 cycle, 3-phase—it is available, however, to operate from any standard voltage.

\*\*Only for the items indicated; remainder of the equipment shown is cooled by Forced Air at 70°±5F. Optionally the items indicated as being water-cooled can *also* be supplied equipped for Forced Air cooling.

### **INSTALLATION REQUIREMENTS**

A motor alternator rated at 8.5 kva furnishes regulated, transient-free 115v 400cycle 3-phase power to the computer. Units are available to operate from the following voltages:

440v 60cycle 3-phase (3-wire) 208v 60cycle 3-phase (4-wire) 208v 400cycle 3-phase (4-wire)

An additional two kva of 115v line-to-line 400cycle 3-phase unregulated power is required to operate the cooling fan. This power may be supplied by the computer generator in installations where the total equipment load does not exceed the rated capacity of the generator. Although the peripheral equipment operates from the same voltage as the computer it should not be connected to the same generator as the computer. This precaution is necessary to prevent transients, resulting from on-off operation of peripheral equipment, reaching the computer memory.

The computer has been designed to be cooled by either water or air. The standard configuration is a water-cooled plenum using approximately seven gallons per minute of 70° F  $\pm$  5° water. An optional air-cooled plenum is available for use in shelters, such as trailers, helihuts, and fixed land-based shelters. Such shelters must be air conditioned (80° F maximum).

Signal interconnection of the units comprising a 1206 system is accomplished through interconnecting cables terminated in connectors which are plugged into mating receptacles at each unit. Power enters the computer through a standard AN connector.

Signal cable of three general types is available to meet various environmental requirements:

Special purpose 40-pair armored cable in accordance with UNIVAC specification DS5177, intended for shipboard service. It conforms as far as possible to Specification MIL-C-915, and has been approved by BuShips for use in the Naval Tactical Data System.

Heavy-duty neoprene jacketed signal cable in accordance with UNIVAC specification DS5215, designed for interconnection of land-based modular shelters such as helihuts or trailers. It is designed to withstand severe flexing and impact loads such as the passage of heavy vehicles over it, and conforms to Specification MIL-C-13777.

Polyvinylchloride-jacketed 40-pair shielded cable in accordance with UNIVAC specification DS5192, intended for installations where severe environmental conditions will not be experienced. It is smaller in diameter than the types listed above, is more flexible, and is considered adequate for land-based installations in the interior of shelters where the ability to withstand severe mechanical abuse is not required.

Special power cable is not required. A standard cable conforming to procuring activity requirements can be selected.

The 1206 dimensions are governed by general shipboard requirements of minimum floor area and maximum height. Dimensions are within the 72-inch maximum permitted by Specification MIL-E-16400. Minimum overhead clearance is 84 inches to permit access to the interconnecting cable receptacles located on top of each unit. The computer design provides front access for normal maintenance; but requires clearance on each side equal to the door width to enable the doors to be swung open for chassis removal.

# APPENDIX A

### **REPERTOIRE OF INSTRUCTIONS AND PROGRAM TIMING**

### INTRODUCTION

This appendix presents the instruction repertoire for the UNIVAC 1206 Military Computer; details presented apply primarily to computer programming. The UNIVAC 1206 is a self-modifying, stored program, one-address computer. Although this means that one reference or address is provided for the execution of an instruction, this reference can be modified automatically during a programmed sequence. Instructions to the UNIVAC 1206 Computer are in the form of 30-bit instruction words stored sequentially in the magnetic core memory; the computer executes the instructions sequentially unless an instruction alters the sequence.

By means of five designators, a computer instruction word completely defines a computer operation. The highest-order six bits of an instruction word constitute the function code designator, f. There are sixty-two function codes each of which corresponds to a machine instruction. The balance of the upper half of the instruction word contains, in the order indicated, the designators j, k, and b. The lower half of the word contains the operand designator, y.

The expression  $Y = y + (B^b)$  relates the **b**- and **y**-designators. The three bits of **b** specify (the address of) the B-register whose *contents* increment **y**; for  $\mathbf{b} = 0$ ,  $Y = \mathbf{y}$ . The precise meaning of Y, for a given instruction word, depends on the function code designator and the value of the operand interpretation designator, **k**.

Normally, the **j**- and **k**-designators are three bits each, however, an input-output instruction requires *four* bits to specify one of the fourteen input channels. This is the four-bit  $\hat{j}$  designator; it is used exclusively with input-output instructions. The resulting operand interpretation designator,  $\hat{k}$ , contains only *two* bits.

Table A-1 briefly describes the operation that corresponds to each of the function codes and indicates the execution times that apply. Table A-2 summarizes the interpretation of  $\mathbf{j}$ ,  $\mathbf{k}$ , and  $\mathbf{\hat{k}}$  with respect to the various function codes. In a particular application of the  $\mathbf{j}$ -designator, not indicated in Table A-2,  $\mathbf{j}$  specifies (the address of) a B-register in each of the four B-box instructions, 12, 16, 71, and 72.

### FUNCTION CODE DESIGNATOR-f

The f designator (6 bits) appears in bit-positions 29 through 24 of the U-register, or an instruction, designating the function to be performed by that instruction. All values of f other than 00 and 77 are defined in the instruction list. The two codes 00 and 77 are *fault conditions* which, if executed, will cause a *fault interrupt*. This results in an interrupt jump to core address 00000, the Fault Entrance Register, or address 00 of *wired* memory, depending on the Automatic Recovery Switch setting (see page A-5).

### BRANCH CONDITION DESIGNATOR-j

The **j** designator (3 bits) appears in bit-positions 23, 22, and 21 of the U-register, or an instruction; it is used in a majority of the instructions. There are three primary categories of use: 1) for Jump, Skip, and Stop determination, 2) for B-register specification, and 3) for repeat status interpretation. Appropriate interpretations of the **j** designator are listed either below or under the descriptions of the individual instructions.

#### Table A-1. UNIVAC 1206 Repertoire of Instructions

BIT ALLOCATION FOR NORMAL INSTRUCTION WORD -k-- b f - i BIT POSITION 06 05 04 03 02 23 07 29 26 2524 22 21 20 18 17 16 15 14 10 09 08 19 13 12 f LÂJ L -b -1 y

### BIT ALLOCATION FOR INPUT-OUTPUT INSTRUCTION WORD

| Image: State of the state | ction<br>cecution<br>node) |      | <b>peat</b><br>esign | Mode     |

|------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------|------|----------------------|----------|

| 00     Illegal Code     Fault Interrupt     0, 4     7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 1                          |      | esign                |          |

| 00     Illegal Code     Fault Interrupt     0, 4     7                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | Other                      | 0 1  |                      | ator     |

|                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |                            | 0, 4 | 7                    | Other    |

| 01 Dight Shift 0 Shift (0) wight by V                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                          |                            |      |                      |          |