## INSTRUCTION BOOK for

## BOGART COMPUTING SYSTEM NAVY MODEL CXPK

## **VOLUME 2 OF 12 VOLUMES**

## SECTION 4 THEORY OF OPERATION

REMINGTON RAND UNIVAC <sup>®</sup> DIVISION OF SPERRY RAND CORPORATION UNIVAC PARK, ST. PAUL 16, MINNESOTA

DEPARTMENT OF THE NAVY BUREAU OF SHIPS

Contract: NObsr 63010 Task: 39 Approved by BuShips: 17 Dec. 1957 I.

### TABLE OF CONTENTS

|      |     |       |                                | Page |

|------|-----|-------|--------------------------------|------|

| 4-1. | Int | roduc | ction to Basic Computer Theory | 4-1  |

|      | a.  |       | eral                           | 4-1  |

|      | b.  | Term  | ns and Abbreviations           | 4-2  |

|      |     | (1)   | Circuit Symbol Assignments     | 4-2  |

|      |     | (2)   | Glossary of Abbreviations      | 4-6  |

|      | C 。 | Fund  | lamentals of Computer Logic    | 4-7  |

|      |     | (1)   | Boolean Algebra                | 4-7  |

|      |     | (2)   | Logical Equations              | 4-10 |

|      |     | (3)   | Magnetic Switch Circuits       | 4-18 |

|      | d.  | Logi  | cal Organization               | 4-43 |

|      |     |       |                                |      |

| 4-2. | Con | trol  | Section                        | 4-43 |

|      | a.  | Gene  | eral                           | 4-43 |

|      | b.  | Mast  | er Clock System                | 4-44 |

|      |     | (1)   | Driver Assemblies              | 4-44 |

|      |     | (2)   | Master Clock                   | 4-45 |

|      |     | (3)   | Resynchronizing Circuits       | 4-53 |

|      | C 。 | Prog  | gram Control                   | 4-57 |

|      |     | (1)   | General                        | 4-57 |

|      |     | (2)   | U-register                     | 4-57 |

|      |     | (3)   | B-Index Registers.             | 4-66 |

|      |     | (4)   | U-Register Adder               | 4-68 |

|      |     | (5)   | P-Register                     | 4-71 |

|      |     | (6)   | Program Control Sequences      | 4-72 |

|      |     | (7)   |                                | 4-73 |

|      | d.  | Prog  | ram Control Circuits           | 4-75 |

|      |     | (1)   | First Level Controls           | 4-75 |

|      |     | (2)   | Second Level Controls          | 4-75 |

|      |     | (3)   | Address Modification           | 4-77 |

|      |     | (4)   | S-Register                     | 4-78 |

|      |     | (5)   | Read Operand Sequence          | 4-78 |

|      |     | (6)   |                                | 4-81 |

|      |     |       |                                | 4-81 |

|      |     | (7)   | Read Next Instruction Sequence | 4-02 |

Page

## TABLE OF CONTENTS (Continued)

|      |    | (8)    | Repeat Sequence               | 4-83  |

|------|----|--------|-------------------------------|-------|

|      |    | (9)    | Skip Sequence                 | 4-84  |

|      |    | (10)   | Normal Jump Sequence          | 4-84  |

|      |    | (11)   | Return Jump Sequence.         | 4-84  |

|      |    | (12)   | Selective Stop Sequence       | 4-85  |

|      |    | (13)   | Master Clear Sequence         | 4-86  |

|      |    | (14)   | Sense A Control               | 4-87  |

|      |    | (15)   | Clear A Control               | 4-87  |

|      | e. | Fault  | Detection                     | 4-88  |

|      |    | (1)    | Main Control Translator Fault | 4-88  |

|      |    | (2)    | Input Fault                   | 4-88  |

|      |    | (3)    | Output Fault                  | 4-89  |

|      |    | (4)    | Load Check Fault              | 4-89  |

|      |    | (5)    | External Fault                | 4-90  |

|      |    | (6)    | Main Fault                    | 4-90  |

|      | f. | 0per:  | ating Controls                | 4-90  |

|      |    | (1)    | Console Control Panel         | 4-90  |

|      |    | (2)    | Indicator Display Panel       | 4-95  |

|      |    | (3)    | Interlock Precautions         | 4-95  |

|      | g. | 0per:  | ating Control Circuits        | 4-95  |

|      |    | (1)    | Back B7 Disconnect Controls   | 4-96  |

|      |    | (2)    | Advance P Disconnect Controls | 4-96  |

|      | ,  | (3)    | Low-Speed Oscillator Controls | 4-96  |

|      |    | (4)    | Trace Jump Control            | 4-96  |

|      |    | (5)    | Selective Jump Control        | 4-97  |

|      |    | (6)    | Fault Controls                | 4-97  |

|      |    | (7)    | Selective Stop Controls       | 4-98  |

|      |    | (8)    | Paper Tape Load Controls      | 4-98  |

|      |    | (9)    | Step Control                  | 4-99  |

|      |    | (10)   | Run Control                   | 4-101 |

|      |    | (11)   | High Speed/Run Control        | 4-103 |

| 4-3. | Ar | ithmet | ic Section                    | 4-104 |

|      | a. | Gene   | ral                           | 4-104 |

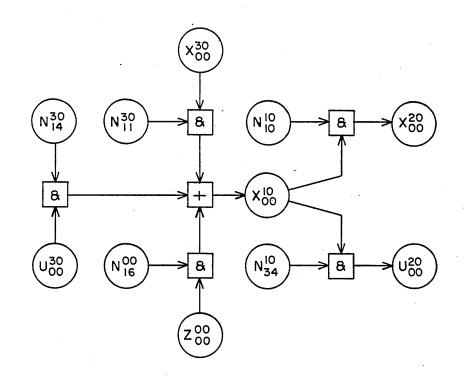

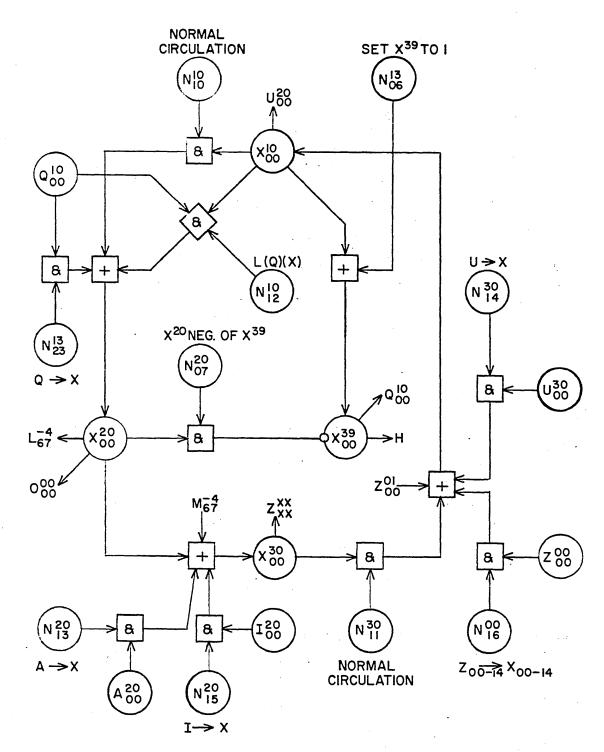

|      | b. | X-Re   | gister                        | 4-105 |

PX 804

## TABLE OF CONTENTS (Continued)

|    |                             |                  |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | Page   |

|----|-----------------------------|------------------|------|---------|------------|----------------|----------------|----------|-----------|-------------|-------------|-----|---|----|---|---|---|--------|

|    | (1)                         | Transm           | issi | ons     | to         | and            | fro            | om (     | x.        | ٥           |             |     | 0 |    |   | • |   | 4-105  |

|    | • •                         | Operat           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-109  |

|    |                             | Operat           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-110  |

|    |                             | - <b>t</b>       |      |         |            |                |                |          |           | J           |             |     |   |    |   |   |   |        |

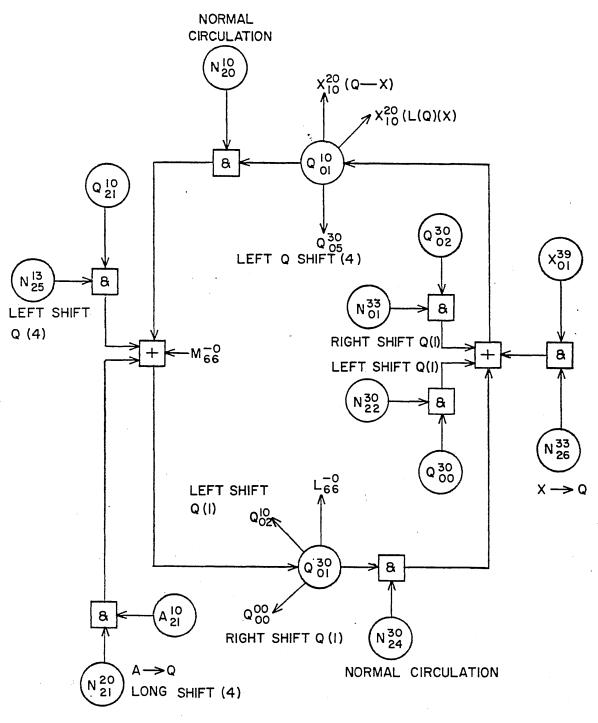

| C. | Q-Reg                       | ister            | o o  | 0 e     | • •        | 0              | 0 <del>0</del> | 0        | 0 0       | ۰           | • •         | • • | 0 | 0  | ٥ | ۰ | 0 | 4-110  |

|    | (1) :                       | Transm           | issi | ons     | to         | and            | fro            | m        | Q.        | •           | • •         |     | ò | 0  | 0 | • | • | 4-110  |

|    | (2)                         | Shifti           | ng   | • •     | • •        | •              | a o            | ۰        | • •       | ٥           | • •         | •   | • | •  | • | • | • | 4-112  |

|    | (3) (                       | Operat           | ion  | as a    | n A        | ssei           | nbly           | 7 R      | egi       | ste         | er .        |     | • | •  | • | • | ٥ | 4-113  |

|    |                             | Operat           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-114  |

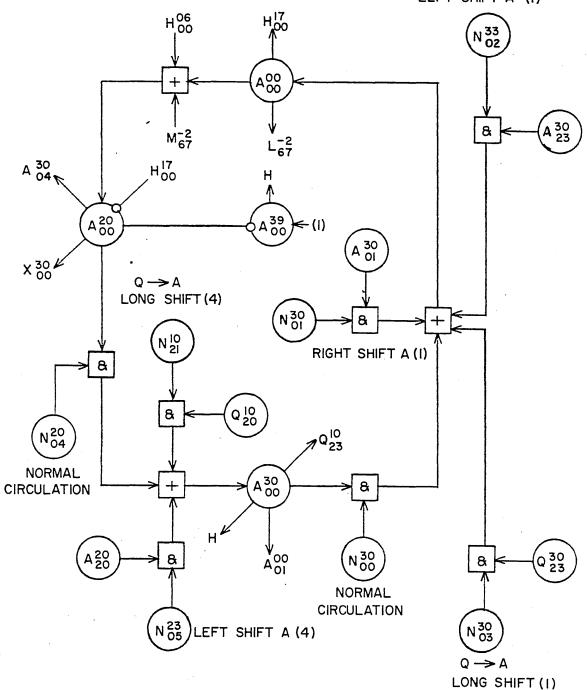

| d. | Accum                       | ulator           | • •  | 0 0     | • •        | o <u>.</u>     | • •            | 0        | • •       | 0           | • •         | • • | • | •  | • | 0 | 0 | 4-114  |

|    | (1)                         | Transm           |      | 0 2 2 2 | + ~        | and            | fme            |          | ٨         |             |             |     |   |    |   |   |   | 4-114  |

|    |                             |                  |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-114  |

|    |                             | Shifti<br>Operat | ny.  | •••     | • •<br>• • | •<br>• • • • • | o o<br>bmat    | °<br>i o | • •<br>Do | 4<br>- 1  - | ()<br>+ ~ ~ | • • | ۰ | ٥  | ۰ | ۰ | 0 | 4-117  |

|    | $(\mathbf{J}) = \mathbf{I}$ | oherar           | 101  | d2 d    | п д        | [11]           | imet           | 10       | лe        | yıs         | 161         | • • | • | ۰  | • | 0 | ¢ | 4-111  |

| e. | Shift                       | Contr            | ol C | ircu    | itr        | у.             | • •            | •        | • •       | o           | •           | • • | • | •  | • | ۰ | • | 4-117  |

|    | (1)                         | Shift            | Coun | ter.    | K-         | Rea:           | iste           | er       |           | ٥           |             |     | ٥ |    | • |   | ٥ | 4-117  |

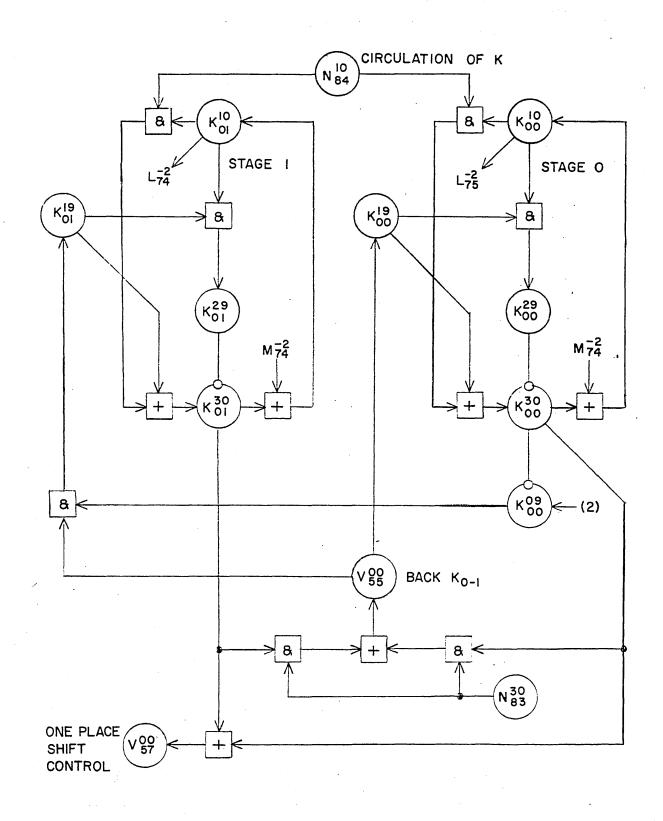

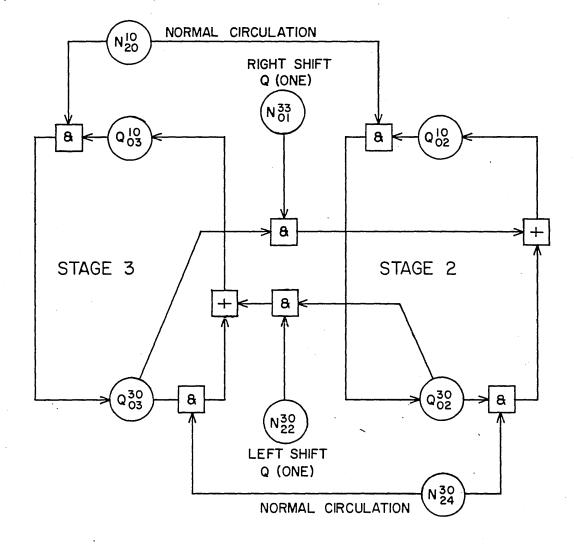

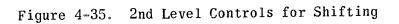

|    |                             | 2nd Le           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-121  |

|    |                             | lst Le           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-121  |

|    |                             | lst Le           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-121  |

|    |                             | Contro           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-123- |

|    |                             | Back K           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-123  |

|    |                             |                  |      |         | • •        | •              |                | •        | • •       | •           | •           | •   | • | •  | • | • | • |        |

| f. | Main A                      | Adder            |      | • •     | • •        | ۰ ،            | • •            | ۰        | ••        | •           | • •         | • • | • | •  | • | • | ٥ | 4-126  |

|    | (1)                         | Basic            | Prop | erti    | es         | of             | the            | Ad       | der       |             | •           |     | • |    |   | • | • | 4-126  |

|    |                             | Logic            |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-126  |

|    |                             |                  |      |         |            |                | -              | -        |           | -           |             | -   | • | -  | • | - | • |        |

| g. | Arith                       | metic            | Sequ | ence    | s.         | •              |                | 0        | • •       | ٥           | • •         | • • | • | ۰  | • | ۰ | ۰ | 4-132  |

|    | (1)                         | Additi           | on.  | o · o   |            |                | • •            | •        |           | •           | •           |     | 0 | •  | • | • | 0 | 4-132  |

|    |                             | Subtra           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-137  |

|    |                             | Nultip           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-139  |

|    |                             | Divisi           | on   |         | • •        |                |                | o        |           | ۵           | •           |     | 0 |    | • | • |   | 4-143  |

|    |                             | Logica           |      |         |            |                |                |          |           |             |             |     |   |    |   |   |   | 4-147  |

|    |                             |                  | ~ ~  |         |            | -              |                | -        |           | -           |             |     | • | -  | - | • | - |        |

| h. | Arith                       | metic            | Sequ | ence    | Co         | ntro           | ols            | 0        | ••        | •           | • •         | • • | • | e. | 0 | ò | ۰ | 4-147  |

v

Page

## TABLE OF CONTENTS (Continued)

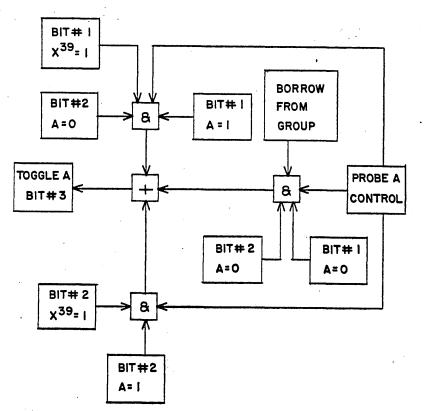

|                                           | ť      | 1) X         | to $x^{3}$          | 9<br>Bufi      | or C  | ontr       | <u>_</u> 1 |              |            |     |     |   |   |     |     |     | 4-147 | , |

|-------------------------------------------|--------|--------------|---------------------|----------------|-------|------------|------------|--------------|------------|-----|-----|---|---|-----|-----|-----|-------|---|

|                                           |        | 2) T         | loggio              | Duii<br>A Cont |       | ,01111     | 01         | • •          | 0          | •   | • • | ۰ | ۰ | •   |     | ۰   | 4-147 |   |

|                                           |        | (3) P        | oggle               | Conta          |       | • •        | 0          | <b>Q</b> . • | ٥          | •   | • • | 0 | e | • • | •   | ٥   | 4-140 |   |

|                                           |        | 3) P<br>3) C | robe A              | CONLI          | .01 ° | • •        | ۰          | • •          | ٠          | •   | • • | 0 | ۰ | • • |     | •   | 4-140 |   |

|                                           |        | (4) C        | omplem              | ent A          | Cont  | Con        | •          | • •<br>1     | 0          | ٩   | • • | 0 | ۰ | •   | • • | •   |       |   |

|                                           |        | 5) S         | et A t              | o Pius         | Une   | e Con      | ιro        | 1.           | ۰          | •   | • • | ٥ | ٠ | •   |     | ۰   | 4-149 |   |

|                                           | -      |              | et A t              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-149 |   |

|                                           |        |              | to X                | 1              |       | • •        |            |              |            |     |     |   |   |     |     |     | 4-150 |   |

|                                           |        |              | let Q <sub>00</sub> |                |       | ntro       | 1.         | • •          | ۰          | 0   | 0 0 | ٥ | ٩ | • • | •   | •   | 4-150 |   |

|                                           |        |              | to X (              |                |       | 0 O        | <b>o</b> - | •            | ٠          | •   | • • | • | ۰ | • • |     | ٥   | 4-150 | 1 |

|                                           | (1     | 0) X         | toQ                 | Contro         | ol.   | • •        | ø          | • •          | •          | ۰   | • • | • | ۰ | • • | • • | ۰   | 4-151 |   |

|                                           | · (1   | 1) L         | ogical              | Produ          | ict o | of Q       | and        | X (          | Cor        | tr  | 01. | ٠ | 0 | •   |     | ۰   | 4-151 |   |

|                                           |        |              |                     |                |       |            |            |              |            |     |     |   |   |     |     |     |       |   |

| 4-4.                                      | Stora  | ge Se        | ction               | •••            | • •   | 6 O        | ٥          | ••           | 0          | •   | ••  | • | ۰ | • • | •   | •   | 4-151 |   |

| (                                         | a.S    | torad        | e Addr              | occ Re         | niet  | or         |            |              |            |     |     |   |   |     |     |     | 1-152 |   |

|                                           |        |              | e Tran              |                |       |            |            |              |            |     |     |   |   |     |     |     |       |   |

|                                           | ບູ່ບູ  | ituray       | e IIan;             | SIEL I         | leyis | LET .      | ٥          | 0 0          | o          | •   | ••  | • | ٥ | • • |     | 0   | 4-132 |   |

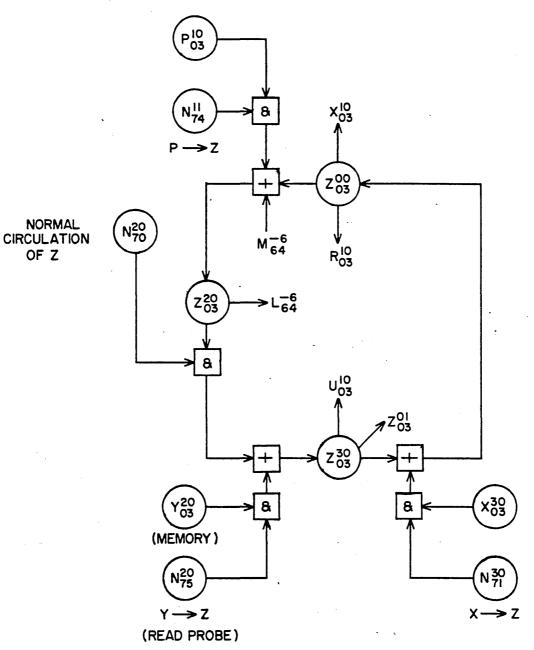

|                                           | τ      | 1) B         | asic P              | ronert         | iec   | of Z       | _          |              |            |     |     |   |   |     |     |     | 4-152 |   |

|                                           |        | (2) Z        | -regis              | tor Bi         | iffor | ,<br>От 51 | •          | • •          | °          | •   | • • | • | • | • • | , . | •   |       |   |

|                                           |        | 3) T         | 'ransmi             | ccione         | , to  | อ่ทส์      | fro        | •••<br>••7   | •          | ۰   | • • | • | • | • • | •   | •   | 4-154 |   |

|                                           | , t    | <b>J</b> ) I | ransmr              | 2210112        |       | anu        | 110        | 11 24        | •          | •   | • • | • | ٥ | 0 ( | • • | •   | 4~104 |   |

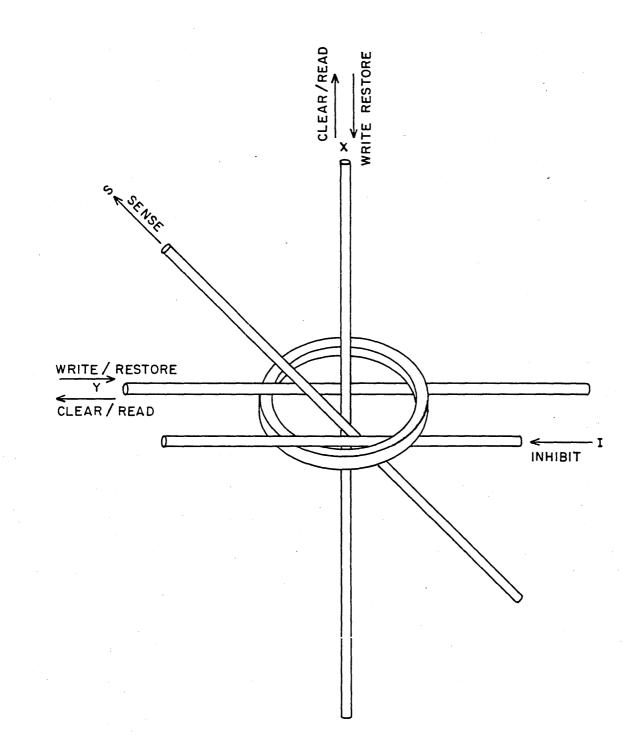

| 1. A. | c. M   | agnet        | ic Cor              | e Star         | ane   | Svet       | em         |              |            |     |     |   |   |     |     |     | 4-157 | • |

|                                           | Uo III | agnet        | 10 001              |                | uge   | 5350       | Cm         |              | ¢          | •   |     | • | ۰ | 0 0 | •   | • • | 4 101 |   |

|                                           | (      | 1) G         | eneral              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-157 | , |

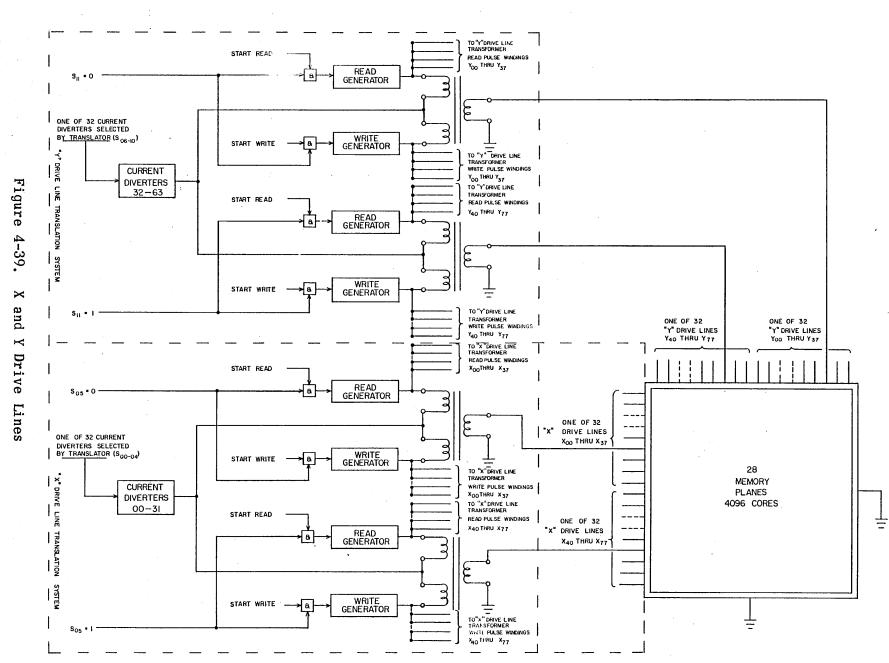

|                                           | -      |              | iemory 1            |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-172 |   |

|                                           |        |              |                     |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-175 |   |

|                                           |        |              | lemory ]            |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-175 |   |

|                                           |        |              | lemory '            |                |       |            |            |              |            |     |     |   |   |     |     |     |       |   |

|                                           |        |              | C Addr              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-183 |   |

|                                           |        |              | C Acce              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-187 |   |

|                                           | . (    | 7) D         | igit P              | lane (         | Contr | °01 C      | irc        | uit          | <b>S</b> . | •   | • • | ٠ | ٠ | 0   | • • | ۰   | 4-191 |   |

| ·                                         | -      |              | ·                   |                |       |            |            |              |            |     |     |   |   |     |     |     |       |   |

| 4-5.                                      | Input  | -Outp        | ut Sec              | tion.          | • •   | • •        | ٠          | • •          | ٠          | •   | • • | 0 | • | • • | • • | 9   | 4-194 |   |

|                                           | -      |              |                     |                |       |            |            |              |            |     |     |   |   |     |     |     |       | : |

|                                           | a. I   | nput.        | • • •               |                | • •   | • •        | ۰          | • •          | ٠          | ۰   | • • | ۰ | • | • • | • • | ۰   | 4-194 |   |

|                                           | ,      | 1) 7         | •                   | <i>•</i>       |       |            |            |              |            |     |     |   |   |     |     |     | 4 705 |   |

|                                           | -      |              | -regis              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-195 |   |

|                                           |        |              | nput S              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-195 |   |

|                                           | -      |              | oad Mo              |                |       |            |            |              |            |     |     |   |   |     |     |     | 4-200 |   |

|                                           |        | 4) C         | -regis              | ter            |       | • •        | •          | • •          | •          | •   | • • | • | • | • • |     | •   | 4-204 |   |

|                                           | (      | 5) E         | xterna              | l Disc         | onne  | ct.        | ٠          | • •          | •          | , ۵ | • • | • | • | •   | • • | •   | 4-205 |   |

|                                           |        | ? <b>.</b> . |                     |                |       |            |            |              |            |     |     |   |   |     |     |     |       |   |

|                                           | b. 0   | utput        |                     | • • •          |       | • •        | •          | • •          | ٠          | •   | • • | • | • | •   | • • | ٠   | 4-205 |   |

|                                           | 1      | 1) ^         | -roai a             | + 0 78         |       |            |            |              |            |     |     |   |   |     |     |     | 4-205 |   |

|                                           |        | 1) 0<br>2) 0 | -regis              | ver<br>Commer  | • •   | • •        | •          | • •          | •          | •   | • • | • | ٥ | • • | • • | •   |       |   |

|                                           | C.     | <u>د</u> ک   | utput :             | sequer         | ice . |            | ٠          | • •          | ۰          | ۰   | • • | ۰ | ٠ | • • |     | •   | 4-207 |   |

PX 804

## TABLE OF CONTENTS (Continued)

|      |     | Pa                                       | <u>ge</u> |

|------|-----|------------------------------------------|-----------|

|      | c.  | External Function                        | 209       |

|      |     |                                          | 209       |

|      |     |                                          | 220       |

|      |     | (3) External Function Sequence 4-        | 211       |

| 4-6. | Pow | ver and Cooling                          | 223       |

|      | a.  | General                                  | 223       |

|      | b.  | Power Supply and Distribution 4-         | 224       |

|      |     | (1) Primary Power Distribution           | 224       |

|      |     |                                          | 227       |

|      |     |                                          | 227       |

|      |     | (4) Central Power Supply                 | 227       |

|      |     |                                          | 228       |

|      |     |                                          | 229       |

|      | C.  | Protective Mechanisms                    | 229       |

|      |     | (1) Overload Protection                  | 229       |

|      |     | (2) Interlocks and Emergency Switches 4- | 230       |

|      | d.  | Cooling System                           | 232       |

|      |     | (1) Description                          | 232       |

|      |     |                                          | 233       |

vii

LIST OF ILLUSTRATIONS

| <u>Figure</u> |                                                 | Page |

|---------------|-------------------------------------------------|------|

| 4-1           | Core Symbols                                    | 4-14 |

| 4-2           | Standard Logic Symbols                          | 4-15 |

| 4-3           | Logic Diagram of the AND Circuit                | 4-17 |

| 4-4           | Logic Diagram of an OR Circuit                  | 4-17 |

| 4-5           | Logic Diagram of an AND NOT Circuit             | 4-19 |

| 4-6           | Complete Stage of the B-Register                | 4-20 |

| 4-7           | Diagram of Magnetic Switch Core                 | 4-22 |

| 4-8           | Hysteresis Loop of Core Material                | 4-23 |

| 4-9           | Phase Relationships of Transfer and Read Pulses | 4-25 |

| 4-10          | Basic Transfer Circuit (B = A)                  | 4-27 |

| 4-11          | Waveforms for Transfer of a "1"                 | 4-30 |

| 4-12          | Waveforms for Transfer of a "O"                 | 4-31 |

| 4-13          | Basic AND Circuit                               | 4-35 |

| 4-14          | Basic OR Circuit                                | 4-36 |

| 4-15          | Basic AND NOT Circuit                           | 4-37 |

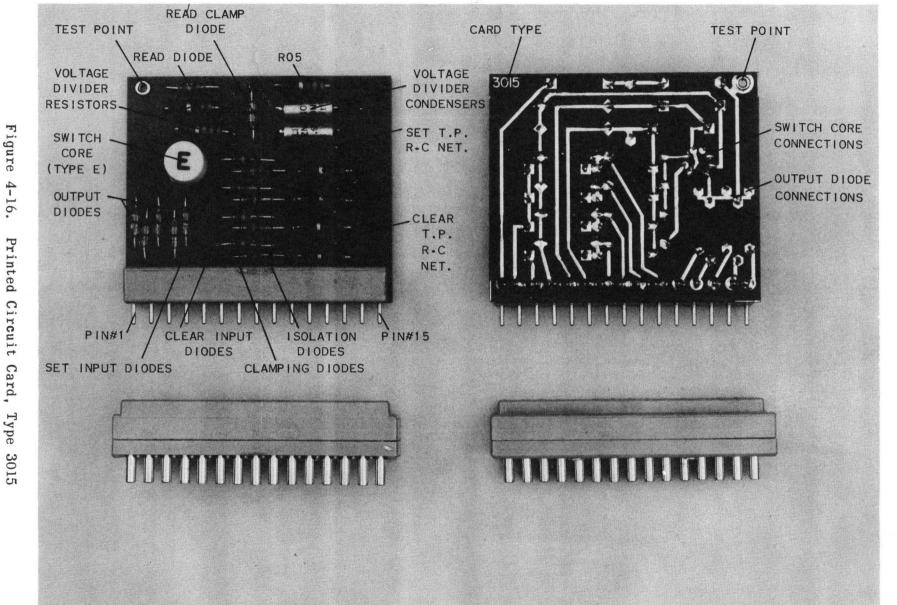

| 4-16          | Type 3015 Printed-Circuit Card                  | 4-39 |

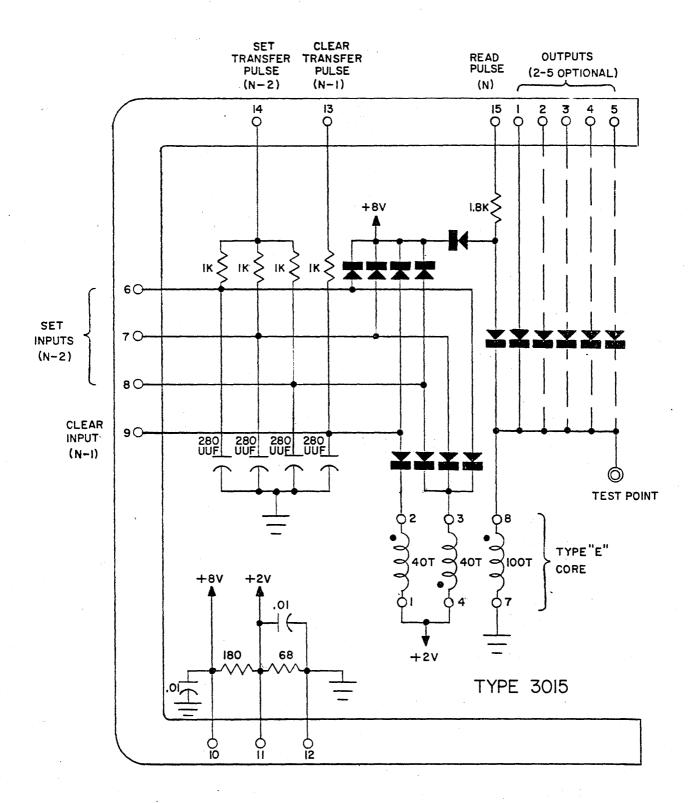

| 4-17          | Schematic Diagram, Card Type 3015               | 4-40 |

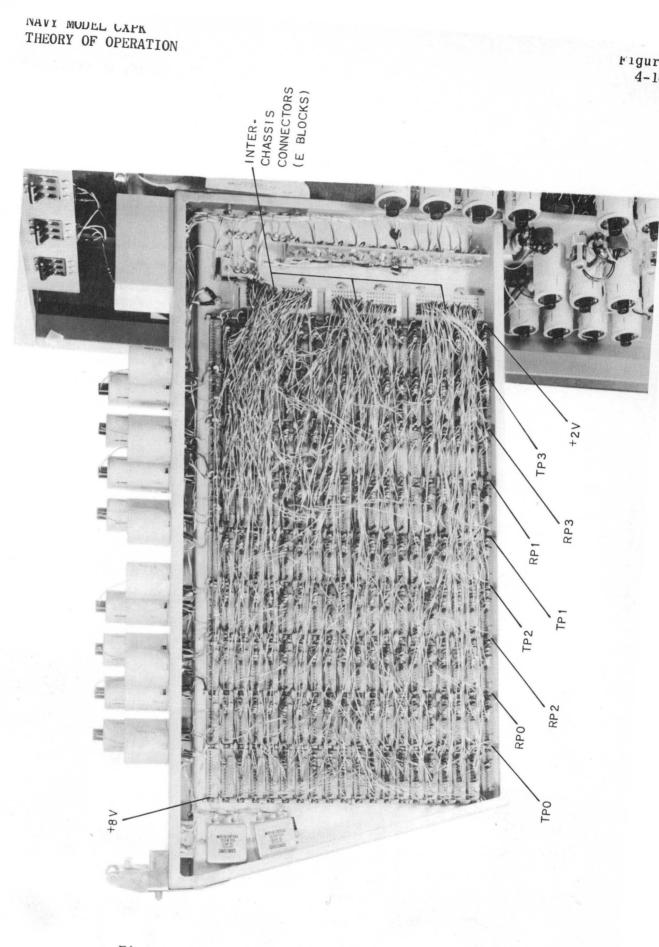

| 4-18          | Standard Chassis, Rear View                     | 4-41 |

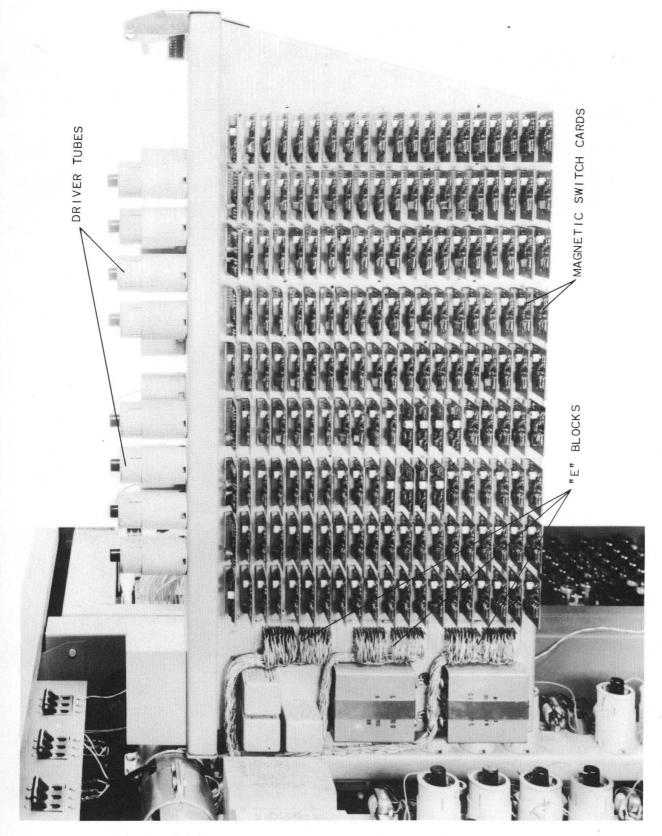

| 4-19          | Standard Chassis, Front View                    | 4-42 |

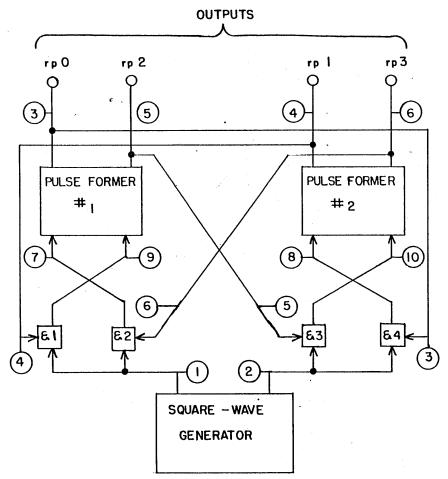

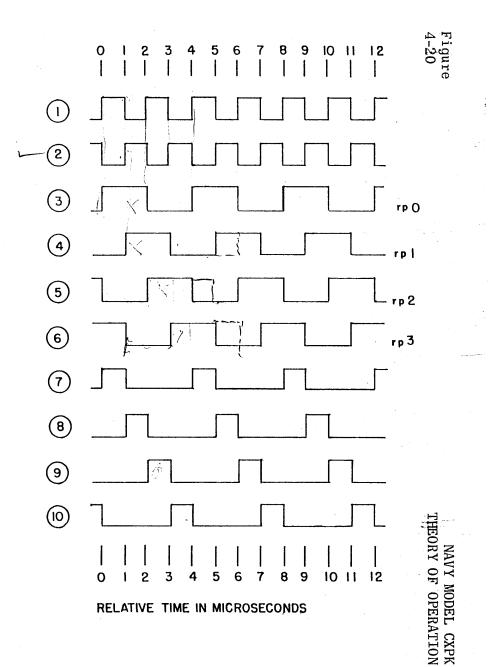

| 4-20          | Clock Timing Diagram                            | 4-46 |

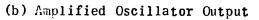

| 4-21          | Clock Oscillator Waveforms                      | 4-50 |

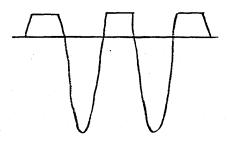

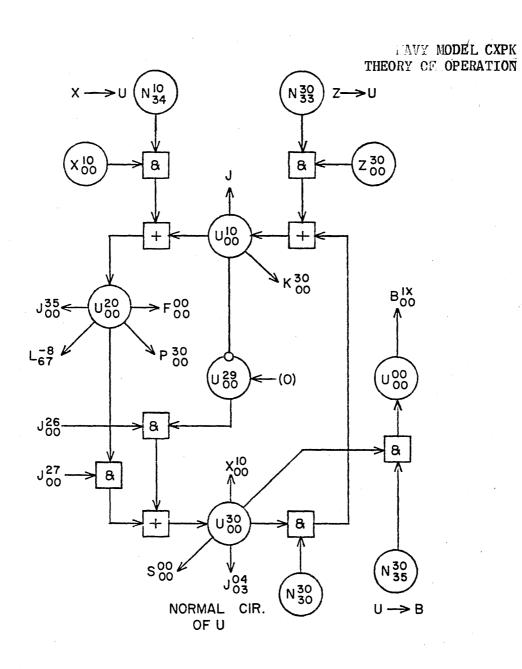

| 4-22          | Twentieth Stage of U-Register ("c")             | 4-59 |

|               |                                                 |      |

•

.

## LIST OF ILLUSTRATIONS (Continued)

| <u>Figure</u> |                                                  | Page  |

|---------------|--------------------------------------------------|-------|

| 4-23          | Portions of An Instruction Word                  | 4-60  |

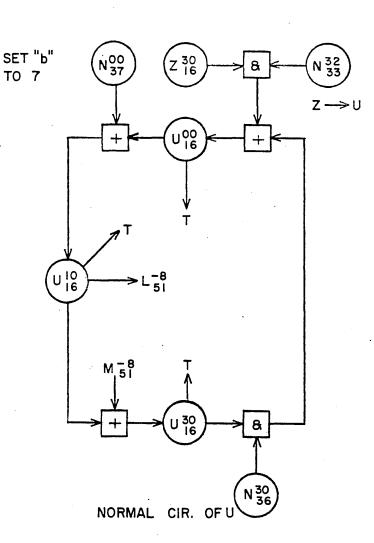

| 4-24          | Seventeenth Stage of U-Register ("b")            | 4-61  |

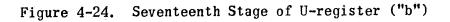

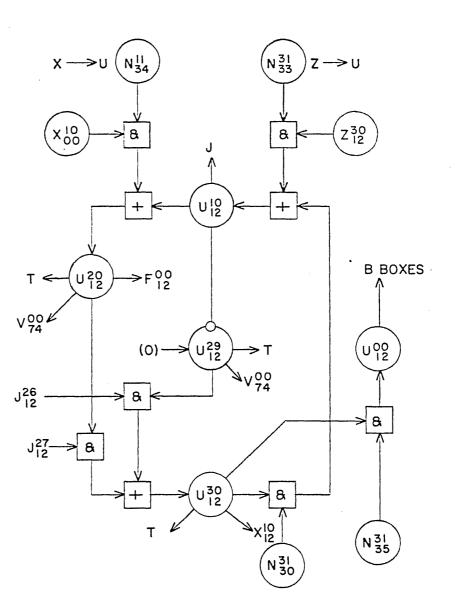

| 4-25          | Twelfth Stage of U-Register ("m")                | 4⊶63  |

| 4-26          | First Stage of U-Register ("y")                  | 4-64  |

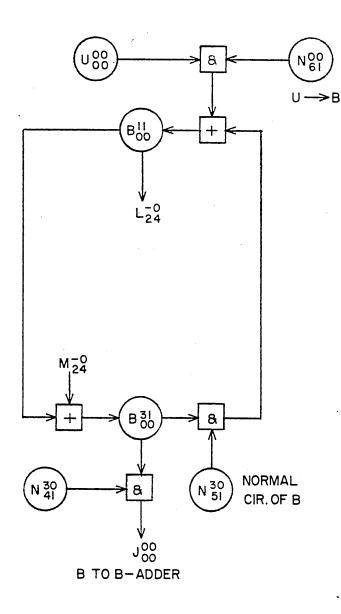

| 4-27          | First Stage of B-box One                         | 4-67  |

| 4⊶28          | Main Control Translator                          | 4-74  |

| 4-29          | First Stage of S-Register                        | 4-79  |

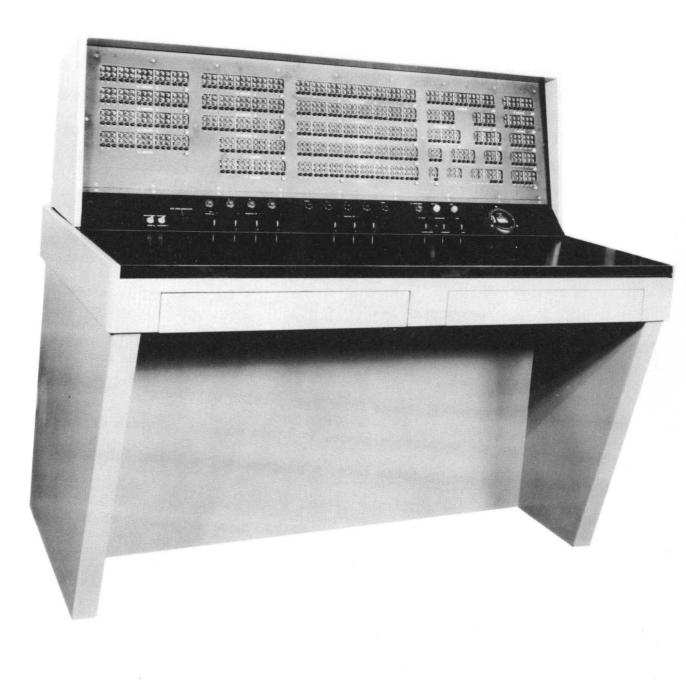

| 430           | Bogart Console                                   | 4-91  |

| 4-31          | First Stage of X-Register                        | 4-106 |

| 4-32          | Second Stage of Q-Register                       | 4-111 |

| 4-33          | First Stage of A-Register                        | 4-115 |

| 4-34          | Shift Counter                                    | 4-120 |

| 4-35          | Second-Level Controls for Shifting               | 4-122 |

| 4-36          | Four-Place Shift Controls (Q)                    | 4-124 |

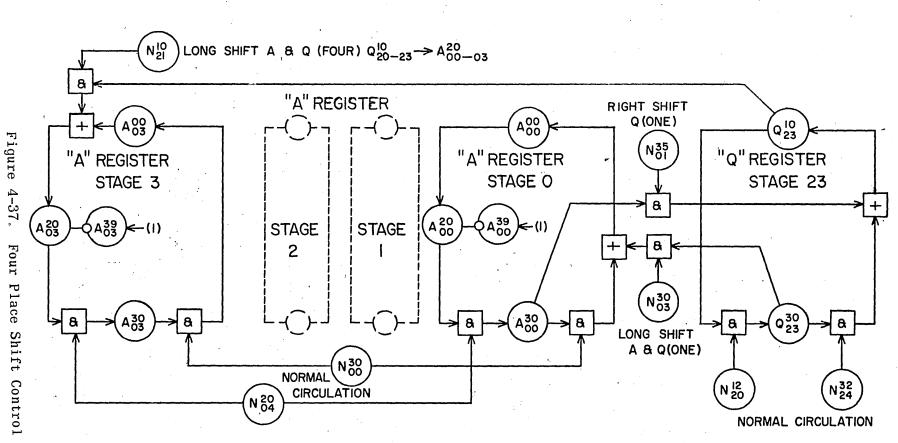

| 4-37          | Four-Place Left Shift Controls (A & Q)           | 4-125 |

| 4-38          | Fourth Stage of Z-Register                       | 4-153 |

| 4-39          | "X" and "Y" Drive Lines                          | 4-159 |

| 4-40          | Typical Magnetic Core and Control Wires          | 4-162 |

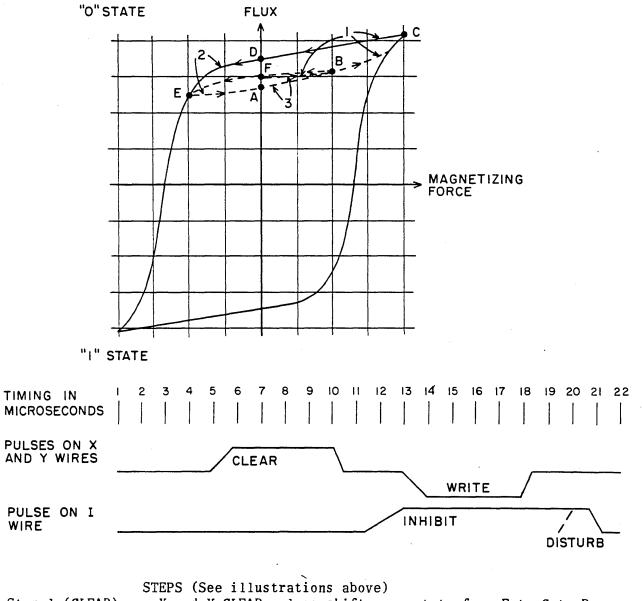

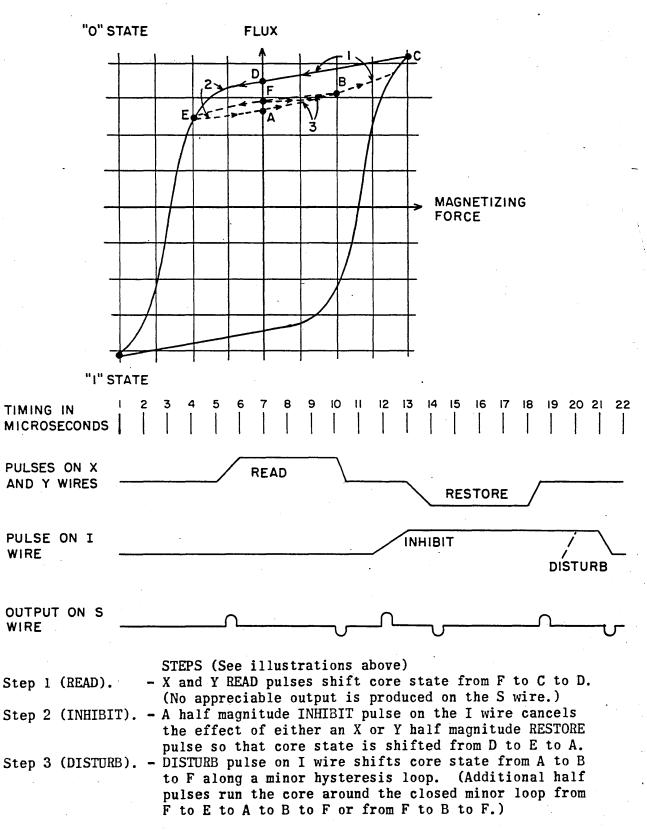

| 4-41          | Writing a "O" When the Core Was in "O" State     | 4-163 |

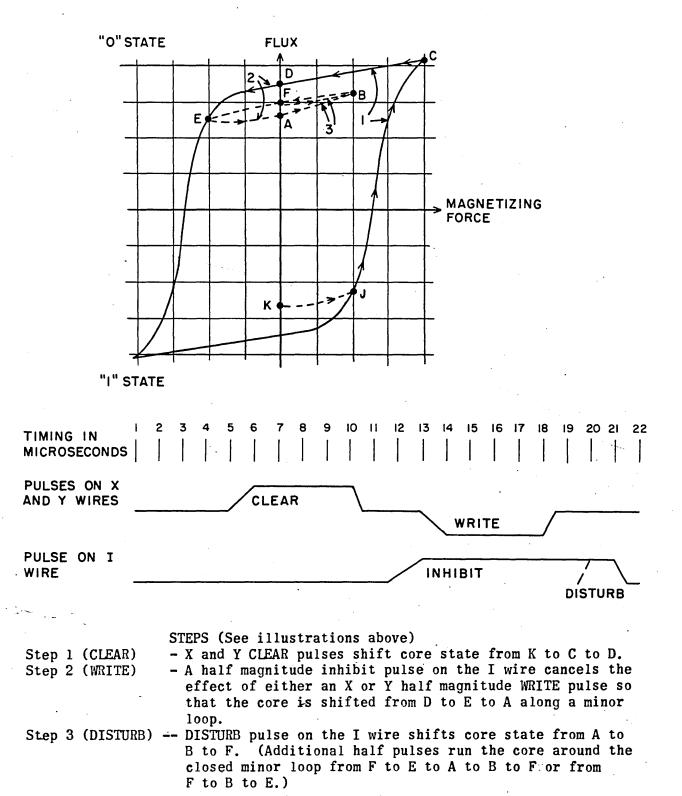

| 4-42          | Writing a "l" When the Core Was in the "O" State | 4-164 |

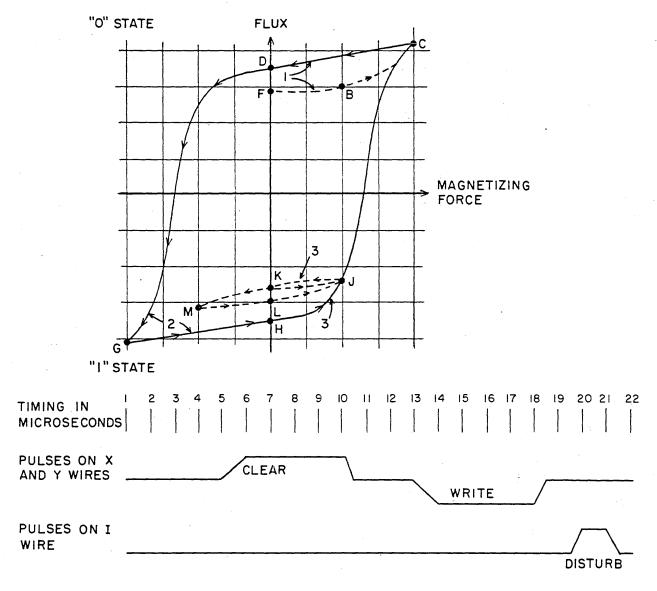

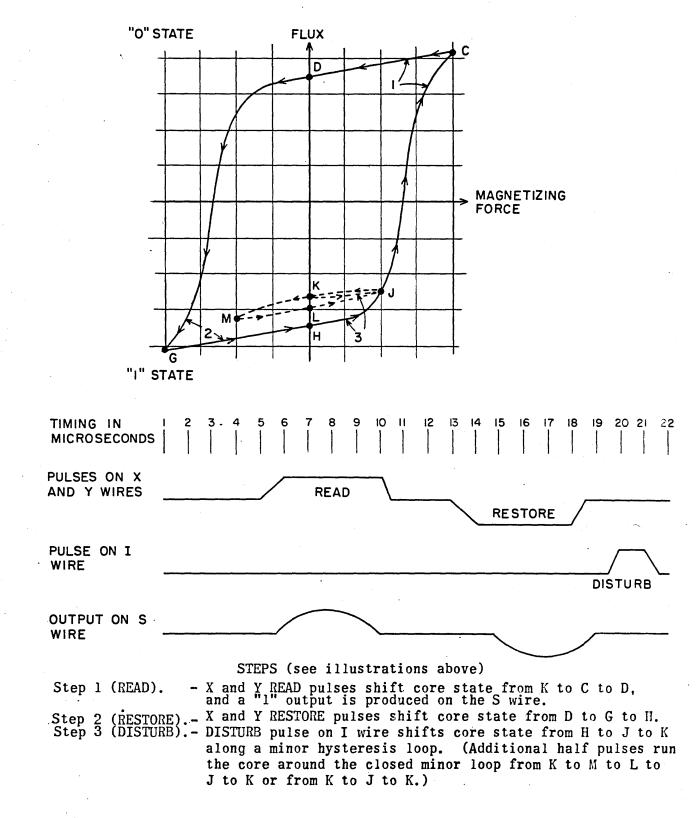

| 4-43          | Writing a "O" When the Core Was in the "1" State | 4-165 |

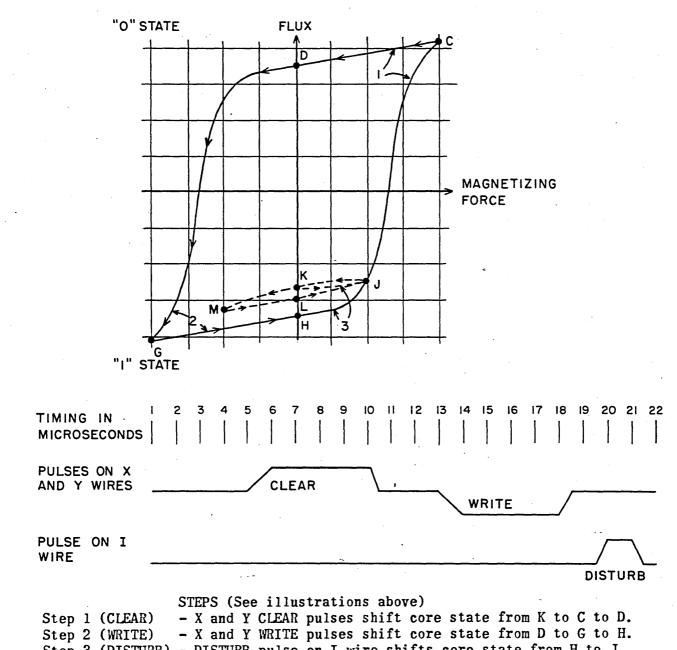

| 444           | Writing a "1" When the Core Was in the "1" State | 4-166 |

| 4-45          | Reading a Core in the "O" State                  | 4-167 |

|               |                                                  |       |

ix

•

х

## LIST OF ILLUSTRATIONS (Continued)

| Figure | 2                                              | Page  |

|--------|------------------------------------------------|-------|

| 4-46   | Reading a Core in the "1" State                | 4-168 |

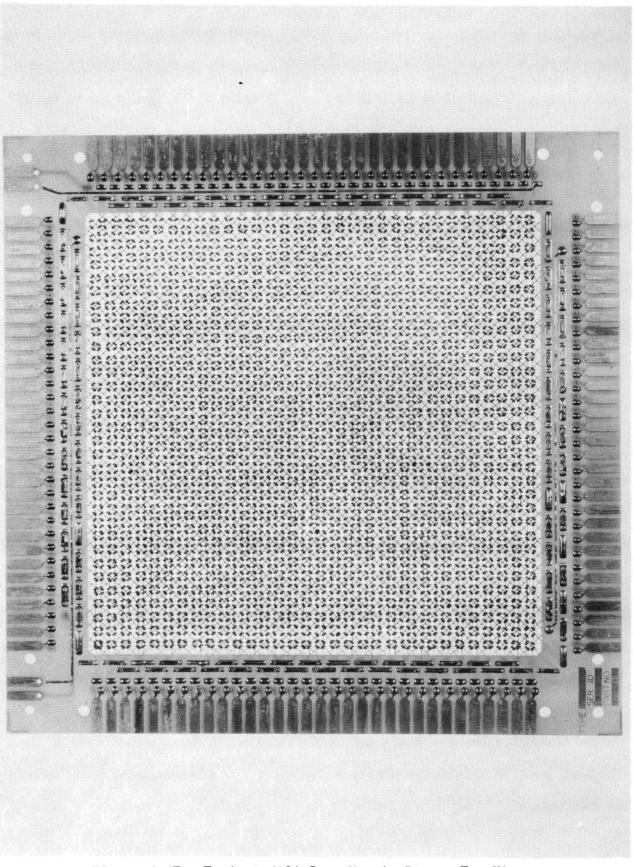

| 4-47   | Typical 4096-Core Matrix Plane, Top View       | 4-173 |

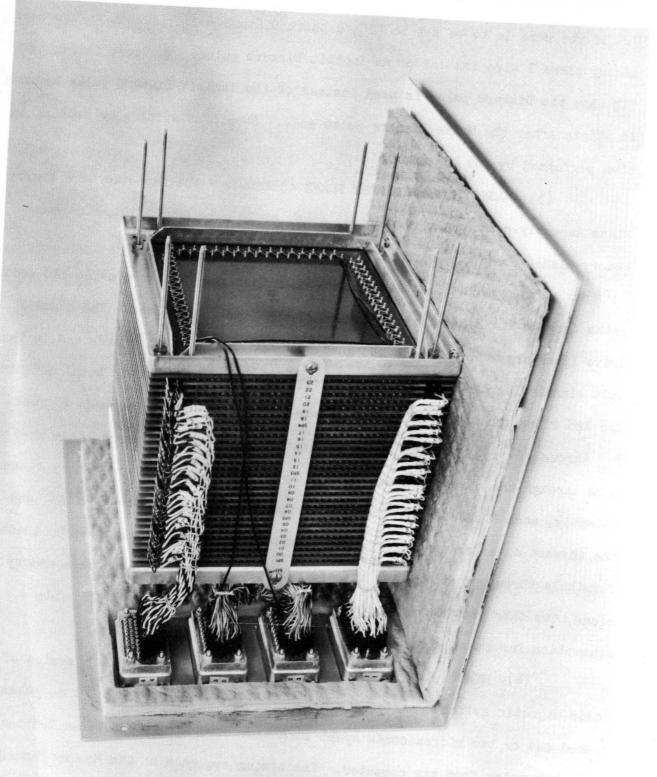

| 4-48   | Magnetic Core Memory Plane Assembly            | 4-176 |

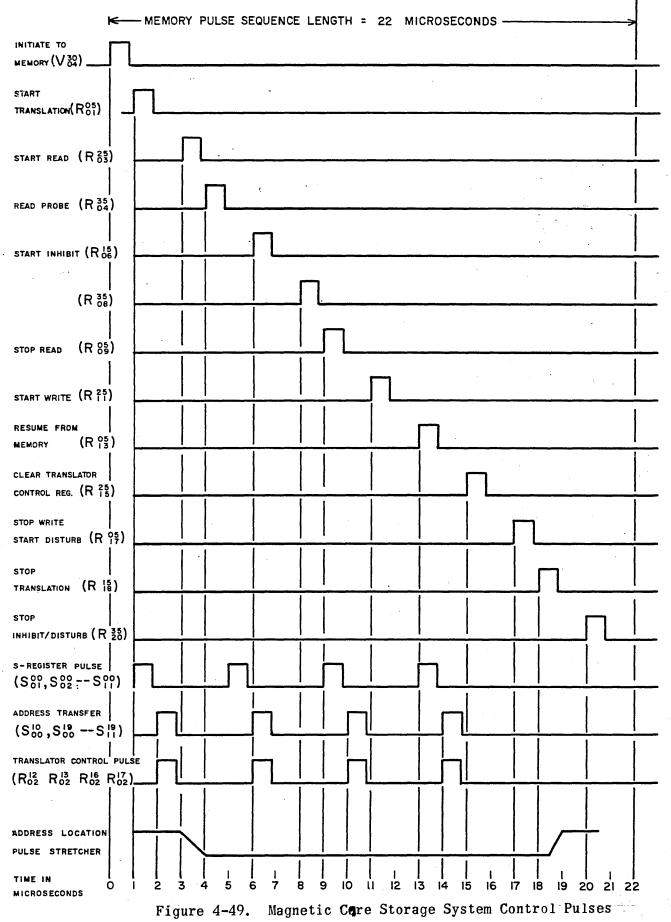

| 4-49   | MCS Control Pulses                             | 4-177 |

| 4-50   | MCS Control Pulses (cont'd)                    | 4-178 |

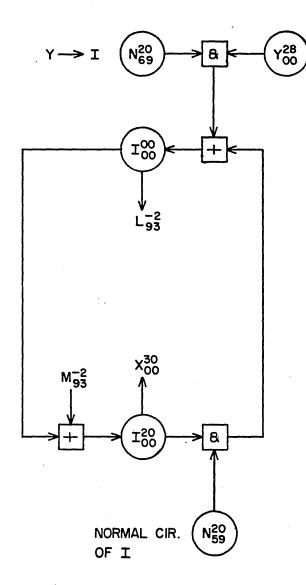

| 4-51   | First Stage of I-register                      | 4-196 |

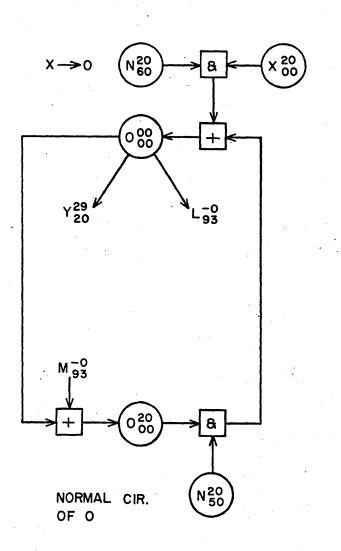

| 4-52   | First Stage of O-register                      | 4-206 |

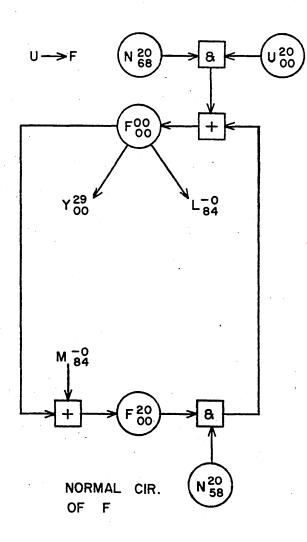

| 4-53   | First Stage of F-register                      | 4-210 |

| 4-54   | Motor-Generator and Exciter Regulator Controls | 4-225 |

# SECTION 4

## THEORY OF OPERATION

4-1. INTRODUCTION TO BASIC COMPUTER THEORY.

a. GENERAL. The Navy Model CXPK (BOGART) equipment is a single-address general-purpose digital computer designed for operation requiring high speed, great programming versatility, and small compact size. Its internal memory consists of a 4096-word magnetic core storage which is capable of storing a 24-bit word as a whole, or any eight-bit third of a word. The eight-bit or third-of-aword feature allows the memory to store a total of 12,288 individual eight-bit words.

The functions of BOGART include manipulating data, differentiating various forms of data and performing analytic, counting, and arithmetic operations. The specific operations which the computer performs are determined by a program which defines the sequence of instructions necessary to execute a desired operation. The computer has a library of 57 instructions available to the programmer (see Volume 1). Most of these instructions can be modified during the operation of the machine by any of seven different B-box registers.

To attain high computing speed, the computer operates in the parallel mode, i.e., all digits of a word are operated upon simultaneously. Internal arithmetic operations are in the binary system. The basic word size is 24 binary digits or bits and this word may be an instruction, operand, or an arbitrarily coded quantity.

The physical make-up of equipment consists of the main computer in one aircooled cabinet, an operation console, electric typewriter cabinet, paper-tape cabinet, converter cabinet, and other optional external equipment. Communication of the main computer with a variety of optional external equipment is made possible by the use of the External Function Register, Input Register, Output Register and converter. Special features built into the computer allow computation to proceed while a unit of the external equipment is operating.

Y 804

Paragraph 4-la

#### NAVY MODEL CXPK THEORY OF OPERATION

PΧ

804

In this volume the emphasis of explanation is placed on what each circuit does logically rather than how each circuit operates electrically in the accomplishment of its function. This approach is taken because of the relatively simple electronic principles involved. The system generally is built of a great number of similar circuits and stages which are adequately explained in the early paragraphs of this section; thus, a general treatment of computer circuits is given which applies to most of the systems operating within the equipment. Where unique circuits are encountered, their operation is described at the point of use rather than in the general theory paragraphs.

b. TERMS AND ABBREVIATIONS. - Because of the complexity of the computer system and equipment, a thorough knowledge of the terms and abbreviations used is essential to the understanding of the system. Sections covering Circuit Symbol Assignments, Glossary of Special Abbreviations and List of Computer Terms should be read preliminary to the reading of this manual. The List of Computer Terms is included as an appendix to Volume 1.

(1) CIRCUIT SYMBOL ASSIGNMENTS. - Many abbreviations used in this text are the same as those used in the Logic Design Equations (Volume 5). The alphabetical code was assigned to similar circuits within the computer system. The 26 capital letters and 5 lower-case letters are assigned as follows:

#### CIRCUIT SYMBOL ASSIGNMENTS

A -- ACCUMULATOR REGISTER. - The Accumulator, A, is a 24-bit register with multiply step and left shift properties. The A-register has two main functions:

1) As an arithmetic register, A holds the sum, difference, partial product, and partial dividend (and remainder) in the corresponding arithmetic operations.

2) A acts together with Q to form an extended accumulator.

- B -- INDEX REGISTER. The Index Registers are 15-bit, B-box registers (B<sub>1</sub> through B<sub>7</sub>) used to store quantities that modify the m and k portions of the instructions. In addition to the above, during the repeat sequence, B<sub>1</sub> is used as follows: The right 12 bits, k, store the repeat count, while the remaining three bits, m, contain information on whether the address of the repeated instruction is advanced by one, decreased by one, or remains the same for each time the instruction is repeated.

- C -- CLOCK CONTROL. The Clock Control, C is a circuit that controls timing used in the control of all logical circuits.

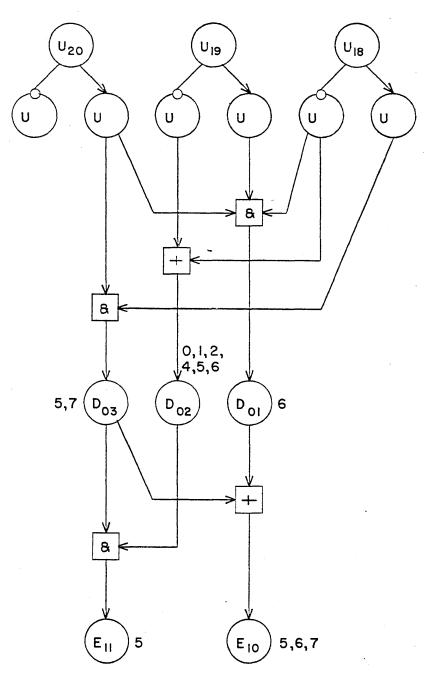

- D -- MAIN CONTROL TRANSLATOR. The Main Control Translator interprets the sixbit c portion of the instruction and sets the appropriate E cores.

- E -- TRANSLATOR CONTROL. The E cores obtain information from the main control translator and are part of the second level control.

- F -- EXTERNAL FUNCTION REGISTER. The External Function Register, F, is a 15bit register that controls selection of input and output equipment.

- G -- OPERATING CONTROLS. The Operating Controls consist of the Run, Step, High-Speed, and Re-sync circuits.

- H -- MAIN ADDER. The Main Adder is used to add the contents of X to A.

- I -- INPUT REGISTER. The Input Register, I, is a seven-bit register used as a temporary storage for data received from input equipment.

- J -- U-REGISTER ADDER. The U-register Adder is used to add the contents of B to U.

- K -- SHIFT COUNTER. The Shift Counter, K, is a six-bit counter-register used to control shifting operations.

- L -- INDICATOR LIGHTS. The indicator lights are located on the indicator display panel and show the contents of the registers.

PX 804

ΡX

804

- M -- MANUAL SWITCHES. These switches are found on both the control panel and indicator display panel.

- N -- FIRST LEVEL CONTROL. The first level control, N, controls the normal circulation of registers and the control of transmissions between registers.

- 0 -- OUTPUT REGISTER. The Output Register, 0, is a seven-bit register used as a temporary storage for data in transit to the output equipment.

- P PROGRAM ADDRESS COUNTER. The Program Address Counter, P, is a 12-stage additive counter which is used to generate successive addresses at which the instructions of the computer's program can be found.

- Q AUXILIARY ARITHMETIC REGISTER. The Auxiliary Arithmetic Register, Q, is a 24-bit register with both multiply step and left shift properties. Its functions are as follows:

- 1) As an arithmetic register, Q holds the multiplier, quotient, and logical multiplier in the corresponding arithmetic operations.

- 2) As an assembly register, Q is capable of receiving six bits at a time and by shifting, ultimately assembling a 24-bit word. It also can disassemble a word by the reverse process.

- R MAGNETIC STORAGE TIMING. These cores control the transfer of information between the Z-register and the Magnetic Core Storage system.

- S STORAGE ADDRESS REGISTER. The Storage Address Register, S, is a 12 bit register used to store Magnetic Core Storage system addresses while words are being read from or written into storage.

- T -TRANSLATOR. This translator interprets the contents of the m and b portions of the U-register.

- U -- PROGRAM CONTROL REGISTER. The Program Control Register, U, is a 24-bit register composed of the following sections:

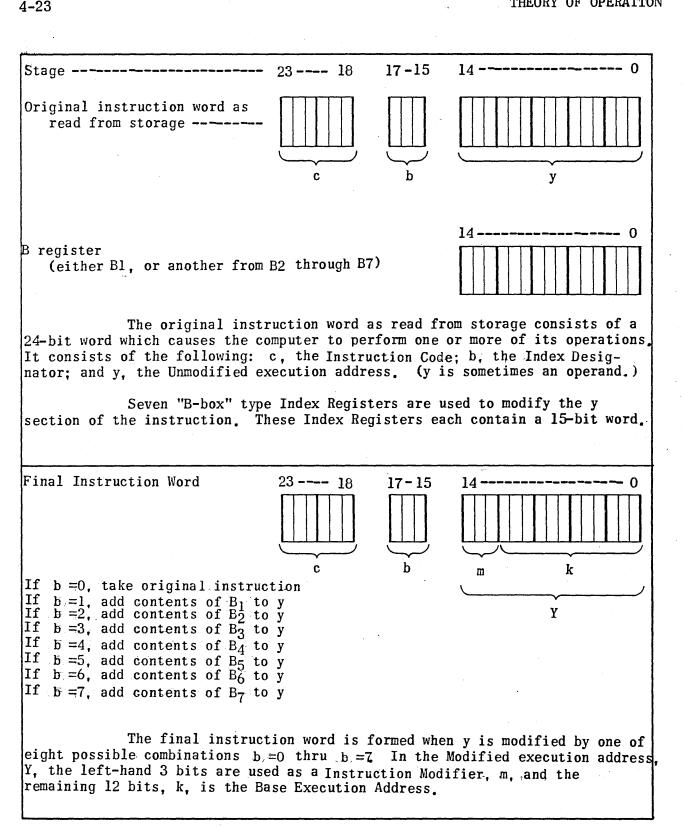

- c -- INSTRUCTION CODE. The Instruction Code, c is a six-bit section consisting of U... U of an instruction word specifying which

of the 57 instruction sequences is to be executed.

- b -- B DESIGNATOR. The Designator, b, is a three-bit section consisting of U ...U of an instruction word which specifies the particular 15 17

B-register (Bl through B7 or none) that is to be used to modify the y portion of the original instruction to obtain Y.

- y -- UNMODIFIED SECTION. The unmodified section, y, is the original U ... U bits of an instruction word.

- Y -- MODIFIED SECTION. The modified section, Y is the 15-bit y as modified by the contents of a B-box specified by the B designator.

- m -- INSTRUCTION MODIFIER. The Instruction Modifier, m, is a three-bit section consisting of U  $_{12} \cdots _{14}$ , and is obtained after modifying y. The Instruction Modifier, (m=0 to m=7) may be used as a Storage Field designator which specifies the particular portion of the operand which will be used in the execution of the instruction. This enables the computer to operate on a 24-bit word or any eight-bit third of a word. Input and Output instructions use the m designator to determine if the whole word, or a section thereof, is to be placed in or taken from memory.

As an Instruction Modifier, m, provides a means of obtaining eight optional choices on Jump instructions and Selective Stop. The Instruction Modifier, m, also provides three modifications for the Repeat instruction.

- k -- BASE EXECUTION ADDRESS. The Base Execution Address, k, is a 12-bit

section consisting of U ...U of the modified section Y and has

the following functions:

- 1) Specifies the particular storage address of the operand to be used in the instruction sequence.

804 ΡX

- 2) During a shift instruction, the right 6 bits of k contain the number of shifts.

- 3) The k portion combined with m can be used as operand.

- V -- SEQUENCE CONTROL. These cores are second level controls used to pass information to the first level controls.

- W -- CIRCULATION BIT. The circulation bits are one-stage registers that can be used for time delay.

- X -- EXCHANGE REGISTER. The Exchange Register, X, is a 24-bit register that has the following functions:

- 1) Can be complemented by use of the  $X^{39}$  buffer.

- 2) As an exchange register, X handles nearly all internal transmission of words between various sections of the computer.

- 3) As an arithmetic register, X holds the addend, subtrahend, multiplicand and divisor in the corresponding arithmetic operations.

- Z STORAGE TRANSFER REGISTER. The Storage Transfer Register, Z, is a 24-bit register used as a temporary storage for words being written into or read from the Magnetic Core Storage.

(2) GLOSSARY OF SPECIAL ABBREVIATIONS. - The following system of abbreviations, not included in the Circuit Symbol Assignments, has been developed to facilitate the explanation of the computer logic:

#### GLOSSARY OF ABBREVIATIONS

- (A) The 24-bit word in A

- Instruction A word, represented by i<sub>23</sub>...i<sub>00</sub>, which causes the computer to perform one or more of its operations. It usually consists of an Instruction Code, c, a B Designator, b, an Instruction Modifier, m, and an Execution Address, k L(Q)(X) Denotes the logical (bit-by-bit) product of (Q) and (X)

PX 804

| NAVY MODEL CXPK<br>THEORY OF OPERA | - ulugiuph                                                 |

|------------------------------------|------------------------------------------------------------|

| MC                                 | A prefix denoting Magnetic Core, used to designate signals |

|                                    | belonging to the Magnetic Core Storage System              |

| MCS                                | Magnetic Core Storage System                               |

| MT                                 | Magnetic Tape System                                       |

| NI                                 | Next Instruction                                           |

| Operand                            | A word on which an operation is performed                  |

| (X)                                | The 24-bit word in X                                       |

| (Y)                                | The contents of storage at address Y                       |

| RNI                                | Read Next Instruction                                      |

| Symbols                            |                                                            |

| >                                  | (Arrow) Transmit, such as (Z) X                            |

| ( )                                | (Parentheses) denotes the content(s) of .                  |

| <i>\$</i> .                        | (Prime) denotes "the complement of" such as X , etc.       |

| $\oplus$                           | Denotes the logical (bit-by-bit) sum of two quantities     |

| (A) <sub>i</sub>                   | Initial contents of the Accumulator                        |

| (A) <sub>f</sub>                   | Final contents of the Accumulator                          |

c. FUNDAMENTALS OF COMPUTER LOGIC.

(1) BOOLEAN ALGEBRA. - A brief review of the basic principles of Boolean Algebra is presented because it is extensively used as an aid in the analysis and design of magnetic switch circuits. Boolean Algebra provides a means for:

- 1) representing a switching circuit without drawing the circuit

- 2) quickly finding a multitude of different circuits that will perform any desired switching function

3) the elimination of redundant circuits

With Boolean logic, the circuit designer has a powerful tool to aid in designing new circuits and in simplifying those already in use.

#### Paragraph 4-1c

#### NAVY MODEL CXPK THEORY OF OPERATION

РΧ

804

(a) BASIC SYMBOLS. - In Boolean Algebra there are only two different quantities, or values, which come into consideration; these quantities are "O" and "1". Each of the variables, termed "literals", in the Boolean equation can assume only one of these two numerical values, corresponding to the active "1" state or the passive "O" state. A Boolean expression is a function of one or more literals representing a combination of switching elements. Algebraic operations used in these expressions are multiplication, addition, and negation. The symbols used in the algebra are shown in Table 4-1 (Glossary of Boolean Terms).

Multiplication and addition symbols are used to denote AND and OR respectively, so that many of the rules of conventional algebra may be applied to the expressions. For representing the AND operation by multiplication, parentheses and/or grouping are preferred instead of the dot or X notation. A bar over a letter in a Boolean expression denotes negation.

There are two types of Boolean equations: 1) identities, and 2) transfer formulas. An identity consists of two equivalent expressions separated by an equality sign. For example, the equation (A+B) C = AC + BC is <u>an</u> identity, which states that either A or B in combination with C is equivalent to either A in combination with C or B in combination with C; while on the other hand, the equation C = A + B is a transfer formula, which states that at some particular instant, a 1 is transferred to element C if a "1" is in either element A or B.

(b) BOOLEAN THEOREMS. - A Boolean expression may be reduced to its simplest equivalent by applying the theorems of Table 4-2. This procedure is noteworthy, because it not only provides means of understanding the circuitry, but also provides means of simplifying magnetic switch circuits, thus reducing the number of components necessary to perform the operations specified by a NAVY MODEL CXPK THEORY OF OPERATION

particular transfer equation. For Example, the transfer equation D = AB + B + C can be reduced to its equivalent D = B + C by applying the the theorems of Table 4-2 to eliminate the redundant expression AB. Because the right side of the reduced transfer equation is simpler than the right side of the original equation, a circuit built by using the simplified equation uses less components and yet performs the same logical functions.

The theorems are also applied to convert the final simplified expressions into standard forms, i.e., forms which are more readily adaptable to magnetic switch cores. For example, the transfer equation  $D = AB + C\overline{B}$  can be reduced to the formula D = (A + C) ( $\overline{B}$ ) which is applicable to the magnetic core AND NOT circuit shown in Figure 4-5.

The proofs of these theorems are all of a similar nature. As an example, a simple proof of Theorem 11 is presented below.

Theorem 11 contains three literals, each capable of being in either the "O" or the "1" state. The various combinations of "1's" and "O's" for these literals are listed in the Conditions column of Table 4-3. In the Left-Hand Expression column, the logical value of the left-hand side of the expression for each AEC condition is registered. Similar values also are registered in the Right-Hand Expression column next to each ABC condition, to represent values obtained from the right-hand expression of the theorem. It is apparent that the left-hand and right-hand values are equivalent for each ABC condition; therefore the two expressions are identical.

PX 804

| · | PROOF |     | BLE 4-3<br>THEOREM | 11   |

|---|-------|-----|--------------------|------|

| A |       | (A  | + B) (A            | + C) |

|   | т     | eft | -Hand              |      |

| Conditions<br><u>ABC</u> | Left-Hand<br>Expression | Right-Hand<br>Expression |

|--------------------------|-------------------------|--------------------------|

| 000                      | 0                       | 0                        |

| 001                      | 0                       | 0                        |

| 010                      | 0                       | 0                        |

| 011                      | l                       | l                        |

| 100                      | l                       | l                        |

| 101                      | l                       | l                        |

| 110                      | ··· 1                   | l                        |

| 111                      | l                       | l                        |

(2) LOGICAL EQUATIONS THEORY. - The logical equations which satisfy the basic magnetic switch core circuits are as follows:

C = A C = AB C = A+B C = AB

In each case the left-hand side of the equation is a function of the expression to the right of the equality sign and may have either of the values "O" or "1". Assuming that A, B, and C are cores to which values may be assigned, the value assigned to core C is derived from the logical operation expressed by the particular combination of the cores A and B, each of which may be assigned values of "O" or "1". The equations are termed transfer formulas in which the equality sign indicates the transfer of the value of the expression on the right of the equality sign to the expression on the left of the sign.

#### NAVY MODEL CXPK THEORY OF OPERATION

The logical operations expressed by these equations are as follows:

1) C = A

This is a simple transfer formula in which the assigned value of core A is transferred to core C. Thus, C = A is assigned values as follows:

A C O O L L

2) C = AB (C = A and B)

The function AB is termed an AND expression: A value of "l" is transferred to core C if both of the cores A and B are assigned the value of "l". Thus, C = AB is assigned values as follows:

| A | В  | С |

|---|----|---|

| 0 | 0  | 0 |

| 0 | l  | 0 |

| 1 | () | 0 |

| l | ב  | 1 |

The AND expression may be expanded to include any number of variables to which the values of "0" or "1" may be assigned.

This logical operation is represented by any of the symbols indicating the arithmetic operation of multiplication.

3) C = A+B (C = A or B)

The function A+B is commonly termed an OR expression: A value of "l" is transferred to core C if either (or both) of the cores A or B are assigned the value of  ${}^{12}$ . Thus, C = A+B is assigned values as follows:

| A | В | С |

|---|---|---|

| 0 | 0 | 0 |

| 0 | l | 1 |

| 1 | 0 | l |

| 1 | l | l |

#### Paragraph 4-1c

The OR expression may be expanded to include any number of variables to which the values of "O" or "1" may be assigned.

4)  $C = A\overline{B}$  (C = A and not B)

The function  $\overline{AB}$ , or  $AB^{-1}$  as it is referred to in the following text, is termed an AND NOT expression: A value of "1" is transferred to core C if core A is assigned the value of "1", and core B is not assigned the value of "1"; or, C assumes the value of "1" if both A and NOT B,  $(B^{-1})$ , have the value of "1". Thus C =  $(AB^{-1})$  is assigned values as follows:

| A | В | B⊸ı | С |  |

|---|---|-----|---|--|

| 0 | l | 0   | 0 |  |

| 0 | 0 | l   | 0 |  |

| l | l | 0   | 0 |  |

| 1 | 0 | l   | 1 |  |

The logical AND operation of the expression is represented by any of the symbols indicating the arithmetic operation of multiplication.

(a) APPLICATIONS TO COMPUTER EQUATIONS. - The logical equations discussed previously can be used to express the operations of the magnetic switch core circuitry and indicate the states of the cores involved by assuming the following correlations:

1) Magnetic cores can be in either the "O" or the "1" state.

2) The answer to the question of whether or not a value of "1" is to be transferred to core C is determined by the states of the cores A and B and the logical operations of the functions.

3) The transfer of a value of "1" to core C is accomplished by the coincident application of Read and Transfer pulses to the circuitry.

#### NOTE

THROUGHOUT THE REMAINING PORTION OF THIS INSTRUCTION BOOK, THE BAR NEGATION SYMBOL (EXAMPLE  $\overline{B}$ ) WILL BE REPLACED BY A NEGATIVE SUPERSCRIPT (EXAMPLE  $B^{-1}$ ). THIS SIMPLIFIES WRITING OF EQUATIONS WITH THE ELECTRIC TYPEWRITER

(b) MAGNETIC SWITCH TRANSFER FORMULAS. - A logical equation is used to describe the function of each magnetic switch core. Because of the number of cores in the computer and their operation at four different clock times of a cycle, special symbols, each designating one particular core, are used in these logical equations. All these equations are formulated in one of two standard forms; the terms which express the basic AND and OR circuits have been described previously.

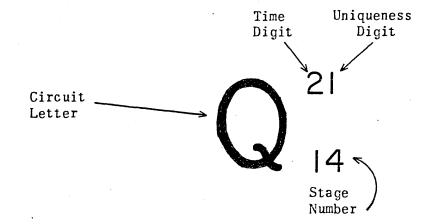

<u>l</u> SYMBOLS. - A typical symbol for a core is shown in Figure 4-1, along with an interpretation of the associated superscript and subscript characters. This symbol is used in the logical transfer formulas to represent a core in the Auxiliary Arithmetic Register (Q).

<u>2</u> STANDARD FORMS OF TRANSFER EQUATIONS. - The standard types of transfer equations are used as follows:

The logical OR expression, C = A + BThe logical AND NOT expression,  $C = AB^{-1}$

Each of these consists of a left-hand term consisting of a symbol for one core, and a right-hand logical expression consisting of not more than four AND clauses, each consisting of not more than four core symbols.

<u>a</u> OR EQUATION. - The OR equation C = A + B is

applicable to a basic OR circuit as shown in examples 1 and 2.

EXAMPLE 1

$X_{00}^{00} = X_{00}^{30} N_{00}^{30} + X_{04}^{30} N_{01}^{30} + X_{08}^{30} N_{02}^{30} + X_{16}^{30} N_{03}^{30}$

EXAMPLE 2

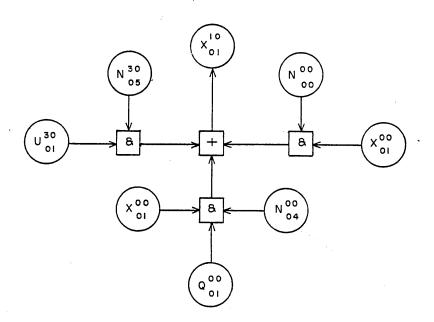

$\mathbf{X}_{\texttt{Ol}}^{\texttt{IO}} = \mathbf{X}_{\texttt{Ol}}^{\texttt{OO}} \mathbf{N}_{\texttt{OO}}^{\texttt{OO}} + \mathbf{X}_{\texttt{OO}}^{\texttt{OO}} \mathbf{Q}_{\texttt{Ol}}^{\texttt{OO}} \mathbf{N}_{\texttt{O4}}^{\texttt{OO}} + \mathbf{U}_{\texttt{Ol}}^{\texttt{SO}} \mathbf{N}_{\texttt{O5}}^{\texttt{SO}}$

PX 804

| Circuit Letter | One letter is used to designate all cores belonging  |

|----------------|------------------------------------------------------|

|                | to a particular register or control system. (Circuit |

|                | letters are listed in Circuit Symbol Assignments.)   |

|                |                                                      |

Stage Number Two subscript numerals indicate the register stage or control circuit subdivision to which a core belongs. For example, in the Q-register, these numbers range from 00 to 23, to correspond with the 24 stages of Q.

Time Digit The first superscript numeral indicates the particular Read Pulse (0, 1, 2, or 3) applied to read the core.

Uniqueness Digit This digit is O unless two or more cores have the same circuit letter, stage number, and time digits. If this condition exists, the symbols are assigned different uniqueness digits so that each core will be represented by a unique symbol.

#### NAVY MODEL CXPK THEORY OF OPERATION

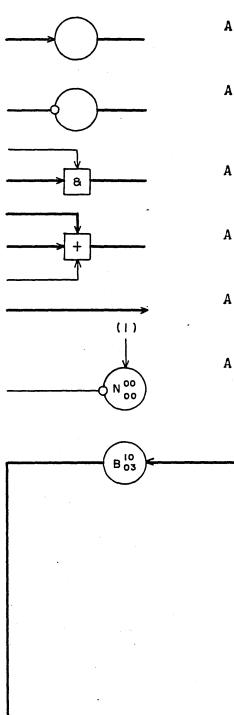

30

- A 1/2 inch circle is used to indicate a magnetic switching core.

- A 3/32 inch circle on the rim of a switching core is used to indicate negation or a logical "NOT" circuit.

- A 1/4 inch square, with (8) inserted, is used to indicate a logical AND circuit.

- A 1/4 inch square, with (+) inserted, is used to indicate a logical OR circuit.

- A heavy inked line terminated by a barbed arrow is used to indicate the path of information.

- A light pencil line terminated by an N core is used to indicate the path of control pulses. Core symbols, and identifying time and stage numbers, are placed within the 1/2 inch circle. An "unconditional set" terminates at the circle with an arrow head, and shows the pulse time (in parentheses) adjacent to the line.

Normal circulation is indicated by a rectangle connecting the cores of any stage in a register.

Information movement is counterclockwise.

#### Paragraph 4-1c

#### NAVY MODEL CXPK THEORY OF OPERATION

In each example, the AND clauses on the right side represent Read outputs from the elements of the clause and Set inputs to the core indicated by the symbol on the left side. Within each AND clause, all symbols have the same time digit. As stated previously in the subparagraph on the basic OR circuit, the operation of the OR circuit is cyclic, and consists of the following steps:

| Time  | n | - | 2   | SET  | INPUTS  |

|-------|---|---|-----|------|---------|

| · · · | n | a | 1 . | SET  | INPUTS  |

|       | n |   |     | READ | OUTPUTS |

|       | n | + | l   |      |         |

By noting the time digits for each of the core symbols, it can be seen that Example 1 satisfies this cycle as follows:

| at ti | me 2 | NO SET INPUTS TO X <sup>OO</sup><br>OO |

|-------|------|----------------------------------------|

|       | 3    | FOUR SET INPUTS TO XOO                 |

|       | 0    | READ X <sup>OO</sup><br>OO             |

|       | 1    |                                        |

Example 2 satisfies the cycle as follows:

| at time 3 | ONE SET INPUT to X <sup>10</sup>  |

|-----------|-----------------------------------|

| 0         | TWO SET INPUTS to X <sup>10</sup> |

| l         | READ X <sup>10</sup><br>Ol        |

| 2         |                                   |

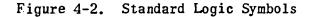

The logic diagrams for these switching circuits are shown in Figures 4-3 and 4-4.

<u>b</u> AND NOT EQUATION. - The AND NOT equation  $C = AB^{-1}$  is applicable to the basic AND NOT circuit. An example is given below.

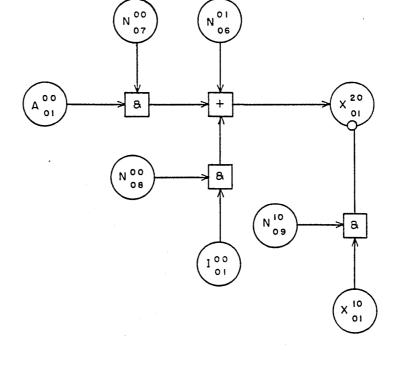

EXAMPLE 3  $X_{O1}^{2O} = \left(N_{OE}^{O1} + A_{O1}^{OO} N_{O7}^{OO} + I_{O1}^{OO} N_{O8}^{OO}\right) \left(X_{O1}^{1O} N_{O9}^{1O}\right)^{-1}$  PX 804

Figure 4-3. Logic Diagram of an AND circuit.  $X_{00}^{00} = X_{00}^{30} N_{00}^{30} + X_{04}^{30} N_{01}^{30} + X_{08}^{30} N_{02}^{30} + X_{16}^{30} N_{03}^{30}$

Figure 4-4. Logic Diagram of an OR circuit.

$\mathbf{X}_{\texttt{Ol}}^{\texttt{lO}} = \mathbf{X}_{\texttt{Ol}}^{\texttt{OO}} \mathbf{N}_{\texttt{OO}}^{\texttt{OO}} + \mathbf{X}_{\texttt{Ol}}^{\texttt{OO}} \mathbf{Q}_{\texttt{Ol}}^{\texttt{OO}} \mathbf{N}_{\texttt{O4}}^{\texttt{OO}} + \mathbf{U}_{\texttt{Ol}}^{\texttt{SO}} \mathbf{N}_{\texttt{O5}}^{\texttt{SO}}$

#### NAVY MODEL CXPK THEORY OF OPERATION

On the right side of this example all AND clauses in the first parenthesis have the same time digits, and all AND clauses in the second parenthesis have time digits one clock time later than the time digits in the first parenthesis. Each AND clause in the first parenthesis represents Read outputs from the elements of the clause and a Set input to the core to the left, and each AND clause in the second parenthesis represents Read outputs from the elements of the clause and a Clear input to the core to the left. The elements of the clause and a Clear input to the core to the left. The -l superscript notation on the second parenthesis denotes negation. The superscript -l notation is the only manner in which negation appears in the logical transfer equations for the computer.

As stated previously in the subparagraph on the basic AND NOT circuit, the operation of the basic AND NOT circuit is cyclic and consists of the following steps:

| Time | n - | 2 | SET INPUTS   |

|------|-----|---|--------------|

|      | n - | 1 | CLEAR INPUTS |

|      | n   |   | READ OUTPUTS |

|      | n + | 1 |              |

By noting the time digits for each of the core symbols, it can be seen that example 3 satisfies this cycle as follows:

| At time | 0 | THREE SET INPUTS to X <sup>20</sup> |

|---------|---|-------------------------------------|

|         | 1 | ONE CLEAR INPUT to X <sup>20</sup>  |

|         | 2 | READ X <sup>20</sup><br>01          |

|         | 3 |                                     |

The logic diagram for this switching circuit is shown in Figure 4-5.

(3) MAGNETIC SWITCH CIRCUITS.

(a) MAGNETIC CORE. - Each magnetic switch contains a core, which is a ring composed of 20 wraps of 1/8 mil thick permanent magnet alloy. PX 804

ı

Figure 4-5. Logic Diagram of an AND NOT circuit.

$$X_{01}^{20} = \left( N_{08}^{01} + A_{01}^{00} N_{07}^{00} + I_{01}^{00} N_{08}^{00} \right) \left( X_{01}^{10} N_{09}^{10} \right) - 3$$

PX 804

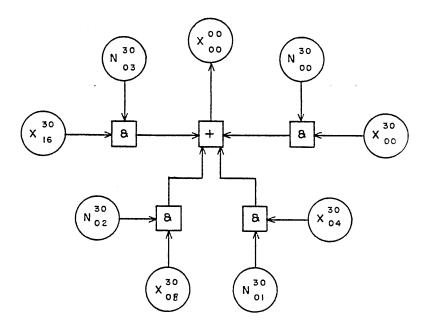

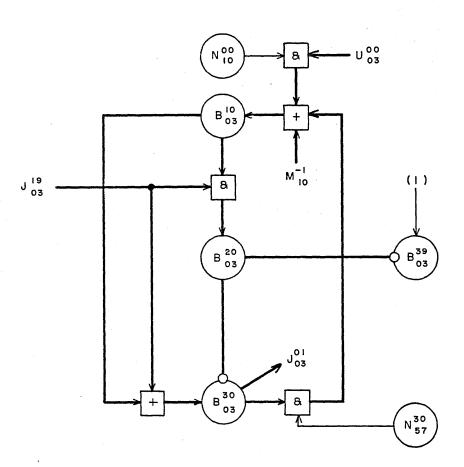

The equations listed below are illustrated above in the typical circuit of a logic diagram.

$B_{03}^{10} = B_{03}^{30} N_{57}^{30} + U_{03}^{00} N_{10}^{00} + M_{10}^{-1}$   $B_{03}^{20} = B_{03}^{10} J_{03}^{19}$   $B_{03}^{30} = (B_{03}^{10} + J_{03}^{19}) (B_{03}^{20})^{-1}$   $--- J_{03}^{01} B_{03}^{10}$   $B_{03}^{39} = (B_{03}^{20})^{-1}$

All cores to the right of the equal sign are considered inputs to the core on the left.

Cores listed in the line below the inputs are considered outputs from the core above on the left.

Figure 4-6. Complete Stage of B-register

804

χd

The ring has an inner diameter of 1/10 inch and a thickness of 1/32 inch. Three wire windings with turns ratios of N:N:2.5N are wound on the core and the entire assembly is potted in casting plastic.

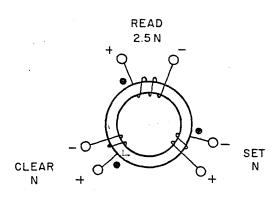

A schematic diagram of a type "E" core assembly is shown in Figure 4-7. The 2.5N-turn winding is called the "read" winding, and the other two are called the "set" and "clear" windings.

The core is a bistable device capable of storing a "1" or "0", depending upon the direction of remanent magnetization in the core. In general, the "0" state is produced when a positive pulse is applied to the "dot" end of a winding (see Figure 4-7), and the "1" state is produced when a positive pulse is applied to the opposite end of the winding. Note that the set winding is of opposite polarity to the read and clear windings.

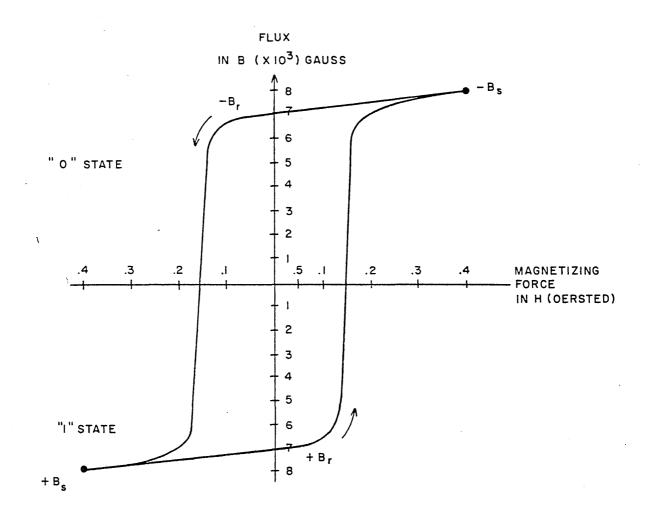

The hysteresis loop for the core material is shown in Figure 4-8.

(b) CRYSTAL DIODES. - Each magnetic switch contains, in addition to the core, from 10 to 15 germanium diodes. The unique property of electrical one-way conduction of diodes makes them useful in the design of logical computer circuits. However, one undesirable characteristic requires special circuit design.

It was generally assumed that germanium diodes would exhibit a large back resistance immediately upon application of a reverse voltage after the diode had been conducting in the forward direction; unfortunately this is not true. Germanium diodes require a finite time to recover to their static back resistance value after reversal of the applied voltage. This time is known as "diode back recovery time".

This enhancement period allows a relatively large decaying reverse current to flow through the magnetic core and may partially reset the core to another value. Where many parallel diodes contribute to this reverse current, as is

Terms:

| READ 2.5 N | - A Read winding of 100 turns                                                  |

|------------|--------------------------------------------------------------------------------|

| CLEAR N    | - A Clear winding of 40 turns                                                  |

| SET N      | - A Set winding of 40 turns                                                    |

| (•)        | - (dot) Used to denote a certain end of the winding.                           |

|            | A positive current applied to the "dot" end of a winding produces a "O" state. |

ļ

A positive current applied to the "opposite" end of a winding produces a "1" state.

PX 8

Figure 4-7. Diagram of Magnetic Switch Core

Terms:

$+B_s$  - Saturation flux density in the "l" direction + $B_r$  - Remanent flux density in the "l" direction - $B_s$  - Saturation flux density in the "C" direction - $B_r$  - Remanent flux density in the "O" direction

Writing a "O".

When a positive current is applied to the "dot" end of the winding, assuming that the core is in the "l" state at  $+B_r$ , the flux state of the core shifts along a major hysteresis loop to point  $-B_r$ . When the positive current is removed, the core shifts to point  $-B_r$  or stable "O" position.

Writing a "1".

804

×

When a positive current is applied to the "opposite" end of the winding (see Figure 4-7), assuming that the core is in the "C" state at  $-B_r$ , the flux state of the core shifts along a major hysteresis loop to point  $+B_s$ . When the positive current is removed, the core shifts to point  $+B_r$  or stable "l" position.

Figure 4-8. Hysteresis Loop of Core Material

#### NAVY\_MODEL CXPK THEORY # OF OPERATION

РХ

804

the case with the output diodes on the magnetic switch printed-circuit card, the reverse drive may be sufficient to completely shift a core.

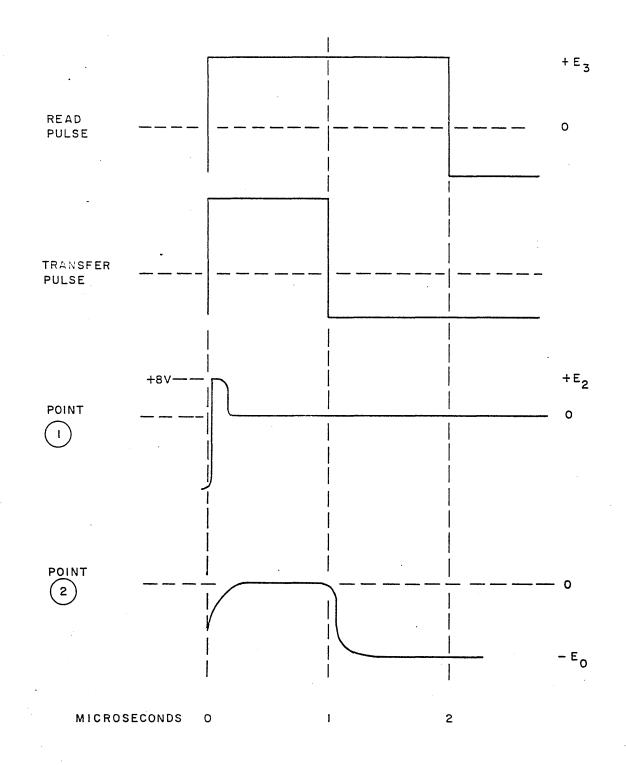

This condition is corrected by deriving a one-microsecond transfer pulse and a two-microsecond read pulse from separate sources. The effect of the enhancement current, caused by the reverse voltage at the end of the transfer pulse, is eliminated by the read pulse existing one microsecond after the termination of the transfer pulse. The characteristic of the diode is such that very little back voltage is generated after one microsecond. With a back recovery time of one microsecond there can be no enhancement current interference after the termination of the two-microsecond read pulse. These pulses are fully described in another paragraph of this chapter.

(c) READ AND TRANSFER FULSES. - The cores in a magnet switch circuit are interconnected so that information is transferred sequentially from core to core by pulses. In each core, the receipt of pulses on the set or clear windings is "remembered" until a pulse on the read winding transmits the remembered bit to the next core.

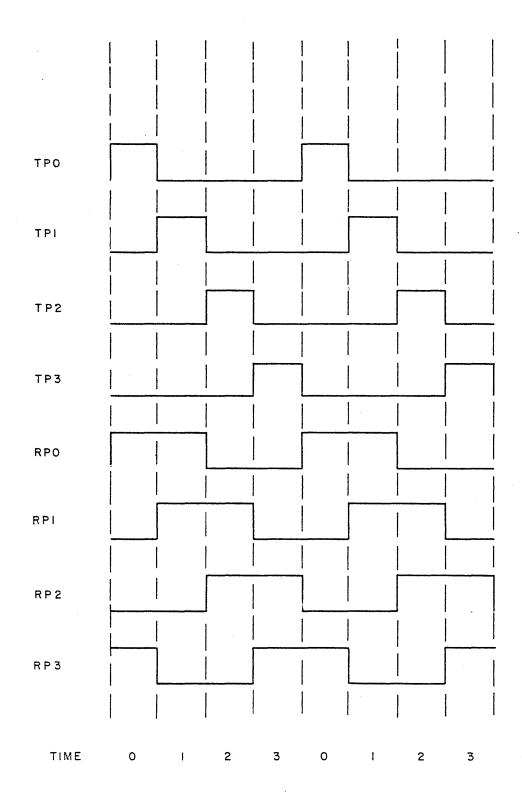

The Set, Clear, and Read operations of the cores are controlled by two types of pulses: Read Pulses and Transfer Pulses. These pulses, distributed to the cores simultaneously, are of a four-phase cycle. During a cycle, each pulse of each type is given a time, denoted by 0, 1, 2, and 3. For example, the four transfer pulse phases of each cycle ard denoted by TFO, TF1, TF2, and TP3. Thus, the sequence of the operations (set, clear, read) of each core is cyclic.

Wave forms of these pulses are shown in Figure 4-9. While no two of the four transfer pulses (TPO through TP3) coincide, it should be noted that the four read pulses (RPO through RP3) overlap by one microsecond. Also note that the first half of RPO coincides with TPO, the first half of RP1 coincides with TP1, etc.

-

Paragraph 4-1c

PX

804

(e) BASIC CIRCUITS.

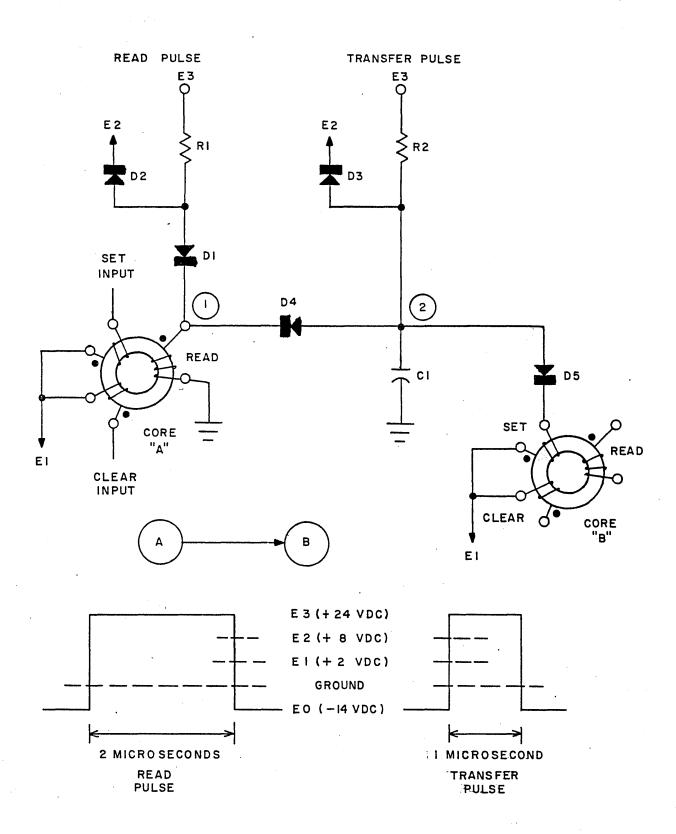

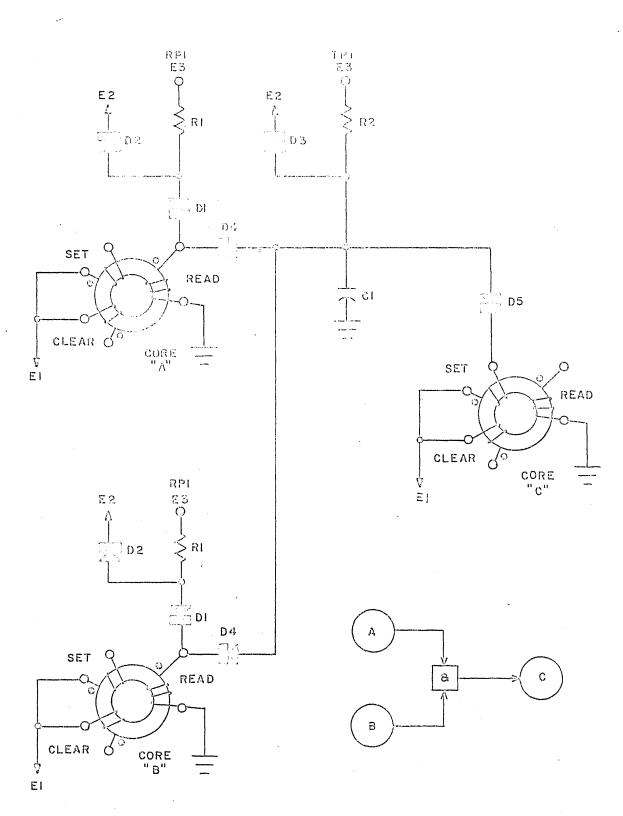

<u>1</u>. BASIC TRANSFER CIRCUIT. - This circuit is a basic block around which all of the other logical circuits are built. The function of this circuit is to transfer the information in core A to core B. Figure 4-10 shows a schematic diagram of the basic transfer circuit. If core A contains a "1", then upon simultaneous application of a read pulse and a transfer pulse, core B is set to the "1" state and core A is cleared to the "0" state. If core A contains a "0", then upon application of the pulses, core B is left in the "0" state and core A is cleared to the "0" state. In either case, B must be initially in the "0" state.

This operation satisfies the Boolean equation B = A, which states that, at some particular instant, B is set to "l" if A contains a "l" or B is left in the "O" state if A contains a "O". The step-by-step operations occurring in the circuit are explained below.

<u>a.</u> TRANSFER OF A 1. - Assume that core A contains a "1" and is therefore at +B on its hysteresis loop, and that core B contains a "O" and is at -B<sub>r</sub> on its B-H loop (see Figure 4-8). Also assume that a positive pulse applied to the dotted end of a core winding produces a flux change in the direction +B<sub>r</sub> to -B<sub>r</sub> and that a positive pulse applied to the opposite terminal produces a flux change in the direction -B<sub>r</sub> to +B<sub>r</sub>.

In the following explanation all references are made to the Basic Transfer Circuit, Figure 4-10, unless otherwise noted.

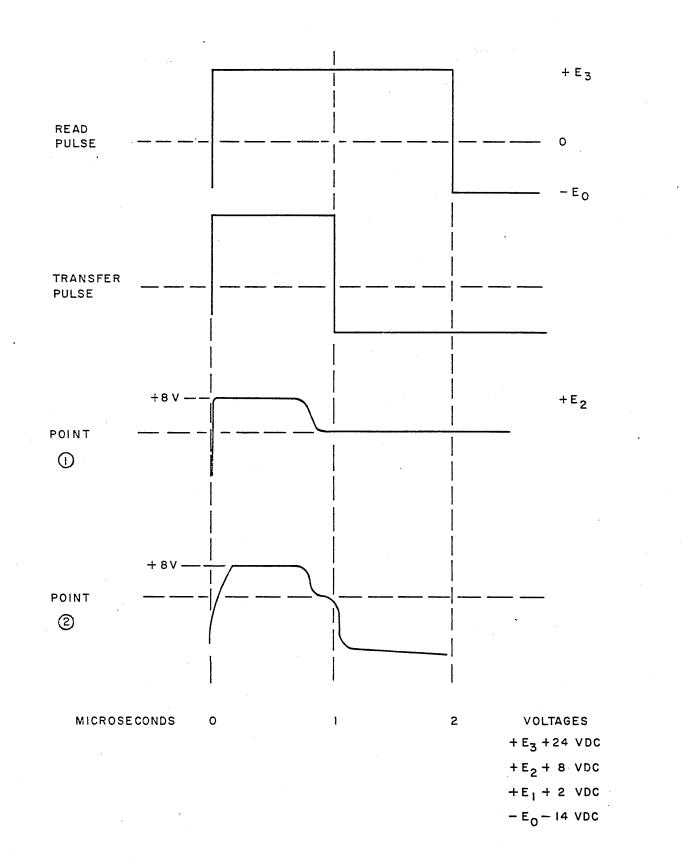

A steeply rising positive (+24 vdc) two-microsecond read pulse, as shown in Figure 4-9, is applied to R. When this clock pulse reaches ground potential, diode Dl conducts and causes a current flow through the 2.5N turn winding on core A. This current causes the magnetic flux in core A to start changing in the direction  $+B_{\rm R}$  to  $-B_{\rm R}$ . The flux changes induce a voltage across Read

Figure 4-10. Basic Transfer Circuit (B = A)

coil A which is clamped at  $E_2$  (+8 vdc) by diode  $D_2$ . Since the 2.5N turn read winding of A is of relatively large inductance, the switching proceeds rather slowly and back emf at point (1) is maintained for about 0.8 microseconds. Point (1) is held at +8 vdc during the entire time core A is switching. When the flux in core A has reached -B, the voltage at point (1) momentarily drops to zero.

A one-microsecond transfer pulse (+24 vdc), occurring during the first half of the read pulse and starting simultaneously with the read pulse, is applied through  $R_2$  to point (2). The voltage at point (2) rises exponentially at a rate determined by  $R_2C_1$ . When this voltage reaches  $E_1$  (+2 vdc), diode  $D_5$ conducts causing core B to start switching from  $-B_r$  to  $-B_s$ . Diode  $D_4$  does not conduct because point (1) is already at +8 vdc. Diode  $D_3$  conducts when point (2) reaches +8 vdc, thus clamping it at +8 vdc. This causes core B to switch at the constant voltage  $E_2 - E_1$  (+60 vdc) until the flux in core B has changed from  $-B_r$  to  $+B_s$ . When the flux in core B reaches  $+B_s$ , the induced voltage in the set winding falls to zero, and point (2) therefore drops to a +2 vdc.

When core A has switched from +B<sub>R</sub> to -B<sub>S</sub> and point (1) is momentarily at ground potential, diode D<sub>4</sub> conducts and point (2) falls below +2 vdc, thus preventing D<sub>5</sub> from conducting. The current then flowing in core A is  $\frac{E_3 + E_3}{R_1} \cdot \frac{E_3}{R_2} \cdot \frac{E_3}{$

<u>b.</u> TRANSFER OF A "O". - Reference is made to Figure 4-10 and 4-12 in considering the case where core A contains a "O" and Core B contains a "O". Under this condition both cores A and B contain a residual flux of  $-B_r$  on their hysteresis loops. It is desired to transfer the "O"

from core A to core B. This is accomplished by creating a minimum disturbance of the magnetic state of core B while core A is being pulsed in the direction  $-B_r$  to  $-B_s$  on its B-H loop, which is the same direction in which core A was pulsed for a "l" transfer.

To cause this transfer a read pulse is applied to core A (Figure 4-10). At the time the read pulse reaches ground potential, diode  $D_1$  conducts, and a current flows in the read coil which produces a flux change in core A from  $-B_r$  to  $-B_s$ . This flux change induces a voltage in read coil A, causing the voltage at point "1" to rise (as shown in Figure 4-12). This voltage will be clampled at E until the flux in core A reaches  $-E_1$ . This switching is completed rapidly so that the voltage at point (1) drops from +8 vdc to ground potential in about 0.1 microseconds and remains there until diode  $D_4$  is caused to conduct by the potential at point (2).

It is for the case of a constant back compacitor  $C_1$  produces its most useful effect;  $C_1$  delays the rise of the transfer pulse voltage at point (2) so that it does not reach ground potential until the voltage at point (1) (produced by the  $-B_r$  to  $-B_s$  flux change in core A) has fallen to zero. The transfer pulse causes point (2) to rise exponentially toward  $+E_s$  at a rate determined by  $R_2 C_1$  until it reaches ground potential. When the voltage at point (2) reaches ground potential, diode D<sub>4</sub> conducts and causes a further flux change in core A. Since core A is already at  $-B_s$ , the flux change is very small, and consequently the voltage pulse produced at points (1) and (2) is very small. No noticeable current from the transfer pulse passes through diode D<sub>5</sub> and therefore no change can occur in core E.

When the read pulse is terminated, core A settles to  $-B_{r}$  (the "0" state) and core B remains in its initial "0" state.

PX 804

Figure 4-11. Waveforms for Basic Transfer Circuit: Transfer of a "l".

**PX** 80,

.

Figure 4-12. Waveforms for Basic Transfer Circuit: Transfer of a "O".

Paragraph 4-1c

## NAVY MODEL CXPK THEORY OF OPERATION

РХ

804

2. CORRELATION OF EQUATIONS AND BASIC CIRCUITS. - The

four-phase cycle timing mentioned previously is an integral part of the operations of each core. Each core has an assigned "read" time; i.e., it receives read pulses from a pulse distributor at only one designated time during a cycle. These Read outputs from a core become inputs to other cores at the same cycle time, or as applied to a logical equation C = f(A,B). Outputs from cores of the terms A and B become inputs to a core C according to the states of the cores of A and B and the logical operations of f(A B). Then at some subsequent assigned time, pulses as applied to a core C become Read outputs from C and inputs to other cores in the circuit. The cyclic operation of the inputs and outputs to a core C as applied to the basic circuits, C = f(A,B), is explained in the following paragraphs.

The read time of a core C is designated as time n of the cycle with the inputs being received at the times n - 1 and n - 2. The time n + 1 is reserved because the readout operation occupies two successive time periods. Therefore, the magnetic switch cannot receive any inputs for two timing periods after the beginning of its read pulse.

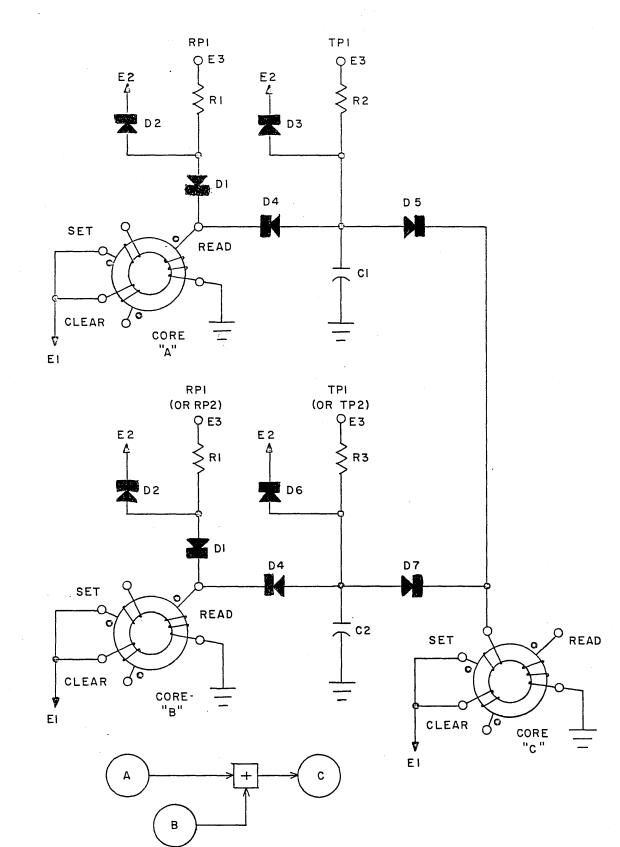

<u>3.</u> BASIC AND CIRCUIT. - The basic circuit for satisfying the logical equation C = AB

where C, A and B represent the cores C, A, and B, respectively, is shown in Figure 4-13. In this circuit, the outputs of A and B are connected directly to the same Set input of C. This circuit can be enlarged so that up to four switch outputs can be connected in an AND union by simply soldering the output lines together.

When the basic AND circuit is used in the four-phase system, all outputs to the AND junction must occur at the same clock time. Thus the timing cycle

for the core C would be as follows:

| Time | n - | 2 | SET INPUTS         |

|------|-----|---|--------------------|

|      | n - | 1 | SET INPUTS         |

|      | n   |   | READ OUTPUTS       |

|      | n + | 1 | 44C) 4338 249 4C8) |

The operation of the circuit shown in Figure 4-13 is as follows: 1) If both A and B contain a "1", their respective output diodes (D4) will be blocked by the emf set up in the read coils, and the TP will be forced through the set winding of C: 2) if, however, either of the input cores contains a "0", the associated output diode will not be blocked, and the TP will be shunted away from the C set winding through the read winding(s) containing the "0".

<u>4</u>. BASIC OR CIRCUIT. - The basic circuit for satisfying the logical transfer equation

$$C = A + B$$

where C, A, and B represent the cores C, A, and B, respectively, is shown in Figure 4-14. This circuit operates on the same principle as the basic transfer circuit, except that the transfer of a "1" to core C can be made from core A or core B, either or both transfers occurring at either of two consecutive times. Outputs from the read windings of cores A and B are connected through a crystal OR circuit to the set winding of core C.

This circuit can be enlarged so that up to four read outputs can be connected as Set inputs to the OR circuitry.

When the basic OR circuit is used in the four-phase system, the timing cycle of the switch C is as follows:

| Time | n | - | 2 | SET INPUT       |

|------|---|---|---|-----------------|

|      | n | - | 1 | SET INPUTS      |

|      | n |   |   | READ OUTPUTS    |

|      | n | + | l | and and can any |

This signifies that the OR circuit can receive one or more Set inputs during any two consecutive clock times, and that a Read output from the core must

PX

804

Paragraph 4-1c

occur immediately after the two times reserved for the set pulses.

Each element A and B of the OR expression could be in itself an AND expression since all Read outputs from an AND equation must occur at the same pulse time.

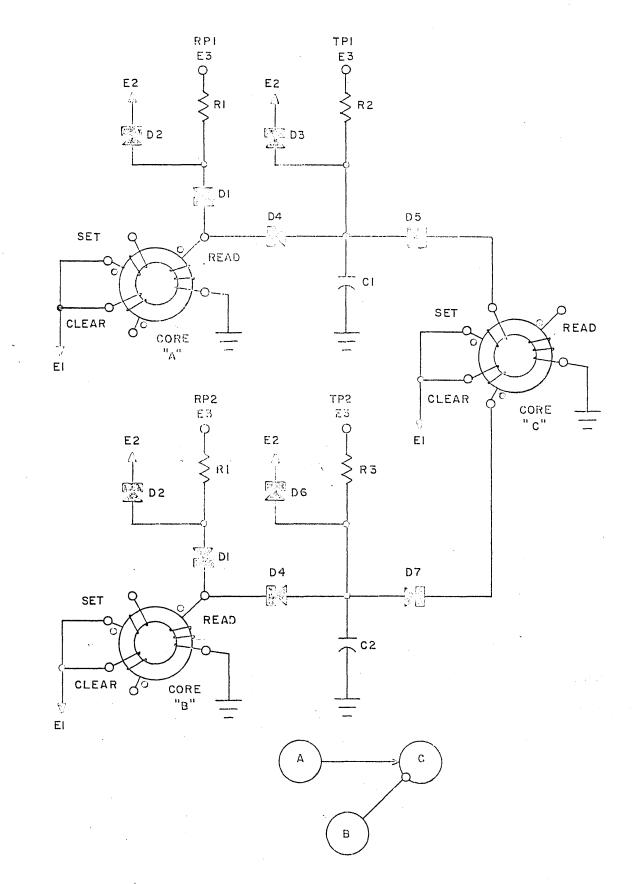

<u>5.</u> BASIC AND NOT CIRCUIT. - The basic AND NOT circuit, shown in Figure 4-15, satisfies the logical transfer equation  $C = AB^{-1}$ where C, A, and B represent the cores C, A, and B, respectively.

This circuit works on a four-phase time negation principle. The timing cycle for the core C would be as follows:

| Time n |   | 2 | SET INPUTS   |

|--------|---|---|--------------|

| 'n     | - | 1 | CLEAR INPUTS |

| n      |   | : | READ OUTPUTS |

| n      | + | 1 | n) m m m m'  |

The operation of the circuit shown in Figure 4-15 is as follows: 1) If A contains a "1", C is set to "1" at time N; then 2) if at time N + 1 B does not contain a "1", C is unaltered.

The elements A and B may be AND or OR expressions if the timing restrictions previously explained for these expressions are adhered to.

Quite frequently it is desired to be able to obtain the complement of a given function. To perform this type of logical operation using magnetic switches, it is necessary unconditionally to set a switch at time n=2, then negate the switch at time n = 1 if the function is "1". If the function is not "1", then this particular switch remains set to "1". This type of circuit satisfies the following logical transfer equation:  $\overline{C} = (1) (B)^{-1}$

(e) APPLICATION TO COMPUTER USE

<u>l</u>. GENERAL. - The smallest physical unit in the computer is the printed-circuit card. The majority of these cards are of the magnetic switch type, in which a magnetic switch core is mounted on a printed-circuit card, along with the crystal AND and OR circuitry associated with the set and

Figure 4-13. Basic AND Circuit:  $C = A \cdot B$

PX 804

ter yr. Syfaar

Figure 4-14. Basic OR Circuit: C = A+B

Figure 4-15. Basic AND NOT Circuit:  $C = (A) \cdot (\overline{E})$

## Paragraph 4-1c

#### NAVY MODEL CXPK THEORY OF OPERATION

clear inputs to the core. One edge of the card is fastened to a 15-pin connector. Thus, to form a circuit satisfying a logical transfer equation, it is only necessary to choose cards having the proper AND and OR input circuitry, plug these into a chassis containing a number of 15-pin jacks, and interconnect the jacks in the chassis.