# SCIENTIFIC

general purpose computer system

# PROGRAMMING

Пананаванерания, Лананав, Шалдочана, мпаном от негат има окончалат

# UNIVAC SCIENTIFIC GENERAL-PURPOSE COMPUTER SYSTEM PROGRAMMING

PX 18

SEPTEMBER 1956

Remington Rand Univac

DIVISION OF SPERRY RAND CORPORATION

# TABLE OF CONTENTS

# PX 33 INTRODUCTION

PX 34 DESCRIPTION OF THE COMPUTER

| 1.  | General                            |

|-----|------------------------------------|

| 2.  | Principal Registers                |

|     | a. X Register                      |

|     | b. Q Register                      |

|     | c. Accumulator                     |

| 3.  | Storage Devices                    |

|     | a. Addressed Storage Locations     |

|     | b. Magnetic Drum Storage System 6  |

|     | c. Magnetic Core Storage System    |

|     | d. A and Q as Storage Media        |

| 4.  | Control Components                 |

| -1. | a. Program Address Counter         |

|     | b. Program Control Registers       |

|     | c. Master Clock                    |

|     | d. Main Pulse Distributor          |

|     | e. Main Control Translator         |

|     |                                    |

|     |                                    |

| _   | g. Program Interrupt Control       |

| 5.  | Representation of Numerical Values |

| 6.  | Arithmetic Operations              |

|     | a. General                         |

|     | b. Addition and Subtraction        |

|     | c. Multiply Sequence               |

|     | d. Divide Sequence 18              |

|     |                                    |

# PX 35 REPERTOIRE OF INSTRUCTIONS

| 1. | Gen | eral                                    | 1        |

|----|-----|-----------------------------------------|----------|

| 2. | Pre | sentation of Instructions               | 2        |

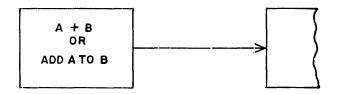

|    | a.  | Transmissive Instructions               | 2        |

|    | b.  | Replace Instructions                    | 4        |

|    | c.  | Split Instructions                      | 4        |

|    | d.  | Q-Controlled Instructions               | <b>5</b> |

|    | e.  | Sequenced Instructions                  | 5        |

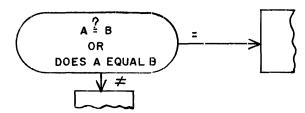

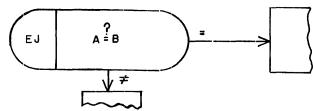

|    | f.  | One-Way Conditional Jump Instructions   | 6        |

|    | g.  | Two-Way Conditional Jump Instructions   | 7        |

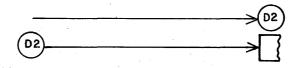

|    | ĥ.  | One-Way Unconditional Jump Instructions | 7        |

|    | i.  | External Equipment Instructions         | 8        |

|    | j۰  | Stop Instructions                       | 9        |

# PX 36 SEQUENTIAL PRESENTATION OF INSTRUCTIONS

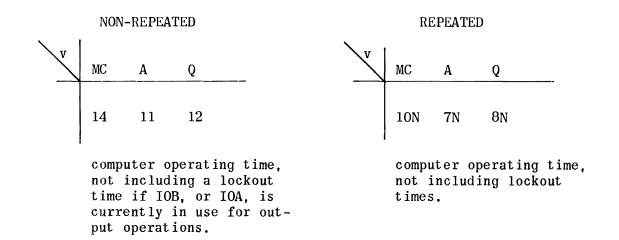

PX 37 INSTRUCTION EXECUTION TIMES

# PX 18

i

# TABLE OF CONTENTS (cont.)

•

# PX 38 INPUT AND OUTPUT SYSTEMS

РX

|    | 1.  | General                               |

|----|-----|---------------------------------------|

|    |     | a. Standard Equipment                 |

|    |     | b. Optional Equipment                 |

|    |     | c. Information Transfer               |

|    | 2.  | Photoelectric Paper Tape Reader 6     |

|    |     | a. General                            |

|    |     | b. Programming for Input              |

|    |     | c. Operation                          |

|    | 3.  | High-Speed Paper Tape Punch           |

|    |     |                                       |

|    | 4.  | Electric Typewriter                   |

|    | 5.  | Punched Card Input/Output System      |

|    |     | a. General                            |

|    |     | b. Programming for Input and Output   |

|    |     | c. Operation                          |

|    | 6.  | Univac Line Printer                   |

|    |     | a. General                            |

|    |     | b. Programming for Output             |

|    |     | c. Format Switchboard                 |

|    |     | d. Operation                          |

|    | 7.  | Magnetic Tape System                  |

|    | -   | a. General Description                |

|    |     | b. Operation Theory                   |

|    |     | c. Tape Operation Timing              |

|    |     | d. Operation                          |

|    |     | e. Improper Programming or Operation  |

|    |     |                                       |

| 39 | OPE | RATING THE COMPUTER                   |

|    |     |                                       |

|    | 1.  | General                               |

|    | 2.  | Operation                             |

|    |     | a. General                            |

|    |     | b. Normal Mode of Operation           |

|    |     | c. Test Mode of Operation             |

|    |     | d. Jump and Stop Selections           |

|    |     | e. Manual Interrupt Selection         |

|    | 3.  | Restoration of Operation After Stops  |

|    | 0.  | a. Programmed Stops                   |

|    |     | b. Force Stop                         |

|    |     | 4                                     |

|    |     | c. Emergency Stops                    |

|    |     | d. Fault Conditions                   |

|    | 4.  | Manual Reading and Writing            |

|    |     | a. Manual Writing from the Q Register |

|    |     | b. Manual Reading from the Q Register |

|    |     | c. Program Correction                 |

|    |     | d. Manual Block Transfer              |

Page

# TABLE OF CONTENTS (cont.)

Page

| PX 40 | CODING FOR THE COMPUTER                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |               |

|-------|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|

|       | <ol> <li>Summary of Machine Characteristics</li></ol>                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 1<br>7<br>7   |

|       | b. Instruction Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | 7             |

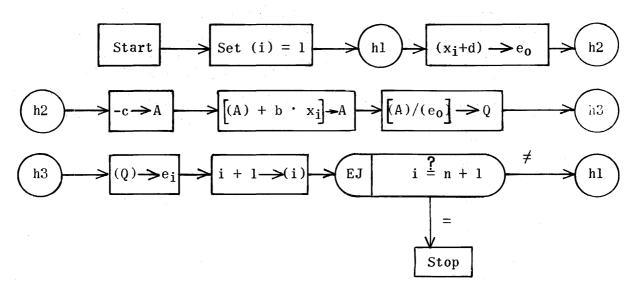

|       | c. Loops                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 8             |

|       | d. Subroutines                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                         | 10            |

|       | e. Relative Addressing                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 21            |

|       | f. Mechanics of Coding                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 23            |

|       | g. Debugging a Program                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 26            |

|       | h. Operating Procedure                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 33            |

|       | 3. Number Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 36            |

|       | a. Introduction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                        | 36            |

|       | b. Radix Conversion                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 37            |

|       | c. Scaling                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 41            |

|       | d. Multiple Precision                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45            |

|       | e. Choice of Number Notation                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                           | 45            |

|       | 4. Notes on the Instructions in the Univac                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             |               |

|       | Scientific Repertoire                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 45            |

|       | a. Operations Involving the Accumulator                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                | <b>4</b> 6    |

|       | b. Shift Instructions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | <b>4</b> 8    |

|       | c. Round Off and Scale Down Operations                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                 | 50            |

|       | d. Accumulative Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               | 51            |

|       | e. Divide Overflow                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                     | 52            |

|       | f. Repeat Instruction                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                  | 53            |

| PX 41 | APPENDIX A - NUMBER SYSTEMS                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                            |               |

| ·     | 1. General.       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       .       . <td< td=""><td><math>\frac{1}{3}</math></td></td<> | $\frac{1}{3}$ |

|       | a. Conversion of Integers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                              | 4             |

|       | b. Conversion of Fractions                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                             | 7             |

|       | 3. Representation of Signed Numbers                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                    | 10            |

PX 42 APPENDIX B - TABLE OF POWERS OF TWO

PX 43 APPENDIX C - DECIMAL TO OCTAL CONVERSION TABLE

# LIST OF ILLUSTRATIONS

| Figure |                                                                                      | Page |

|--------|--------------------------------------------------------------------------------------|------|

| PX 34  | DESCRIPTION OF THE COMPUTER                                                          |      |

| 1.     | Simplified Block Diagram of the Univac Scientific<br>General-Purpose Computer System | . 3  |

| PX 38  | INPUT AND OUTPUT SYSTEMS                                                             |      |

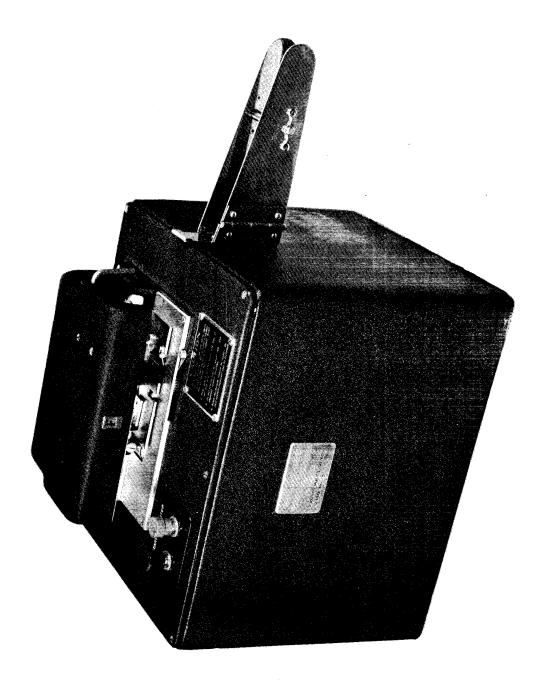

| 1.     | Photoelectric Paper Tape Reader                                                      | . 7  |

| 2.     | High-Speed Paper Tape Punch                                                          | . 11 |

| 3.     | Electric Typewriter                                                                  | . 13 |

| 4.     | Card Unit, Punch Card Input/Output System                                            |      |

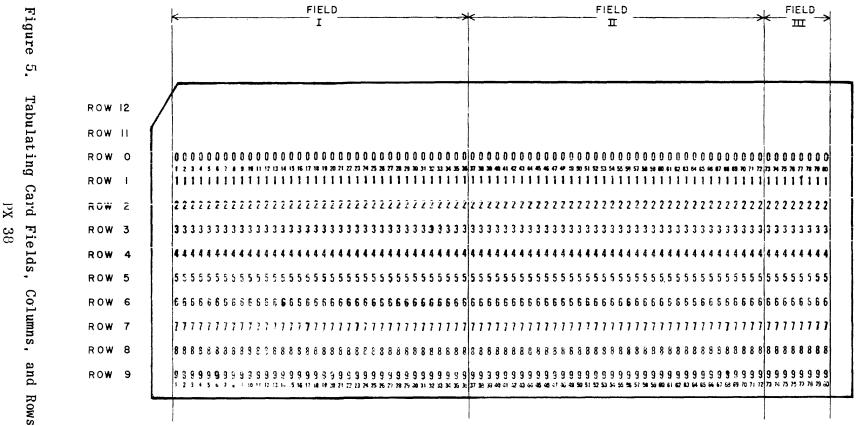

| 5.     | Tabulating Card Fields, Columns, and Rows                                            | . 18 |

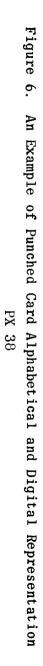

| 6.     | An Example of Punched Card Alphabetical and                                          |      |

|        | Digital Representation                                                               | . 19 |

| 7.     | Univac Line Printer                                                                  |      |

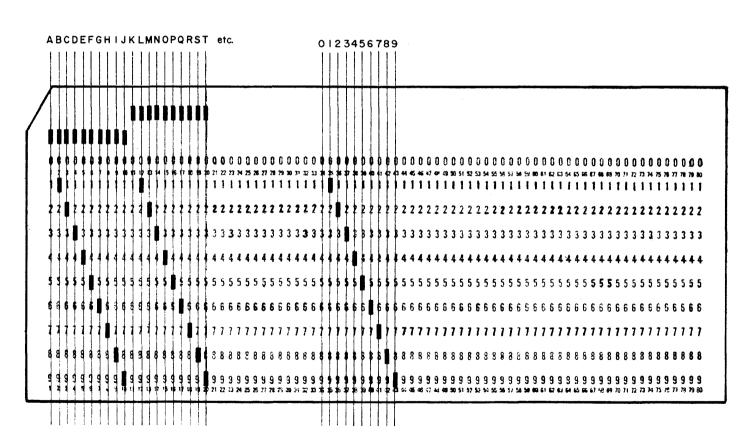

| 8.     | Optional Format for Line Printer Output                                              |      |

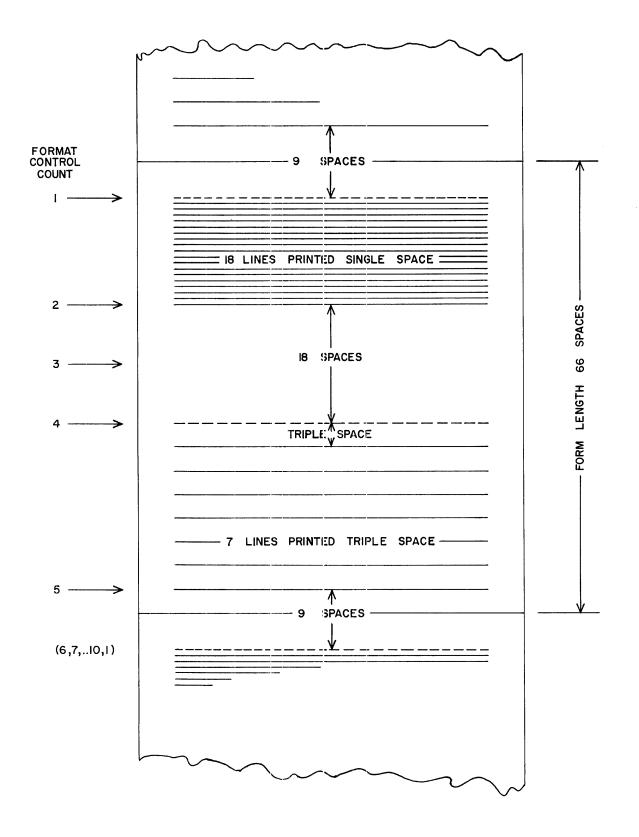

| 9.     | Write Sequence                                                                       |      |

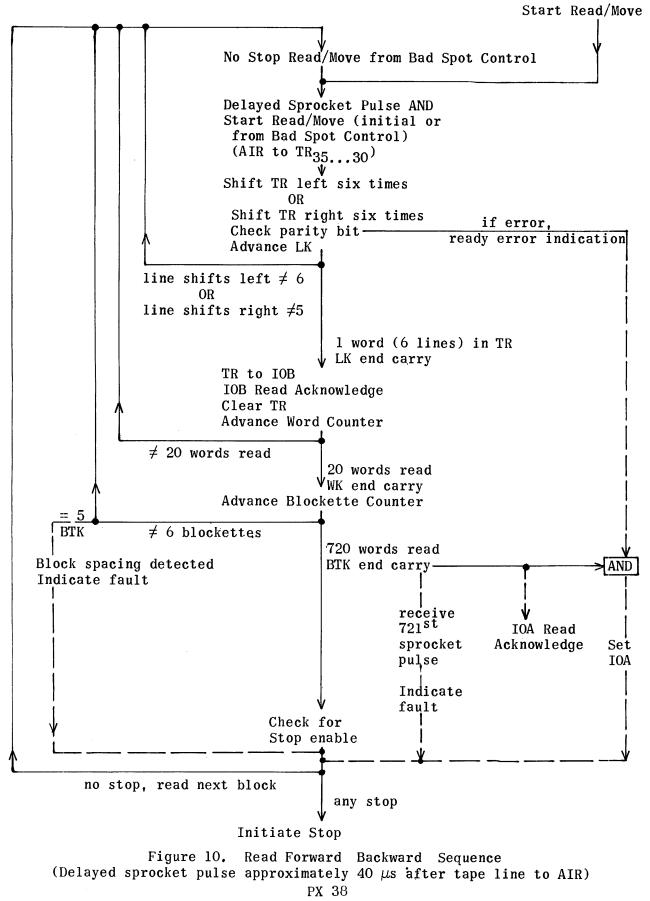

| 10.    | Read Forward Backward Sequence                                                       |      |

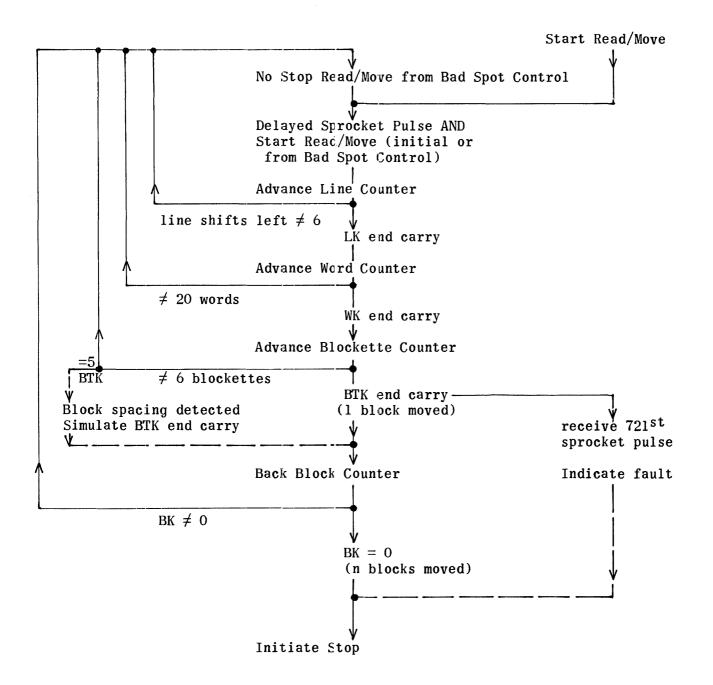

| 11.    | Move Forward or Backward Sequence                                                    |      |

| PX 39  | OPERATING THE COMPUTER                                                               |      |

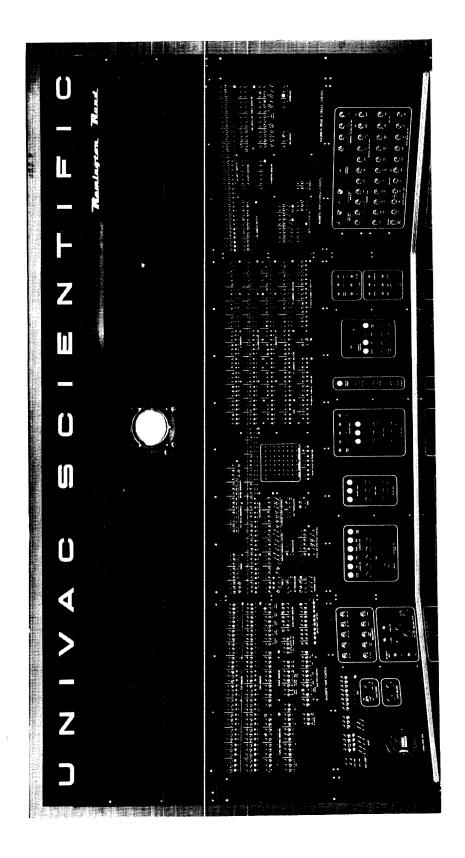

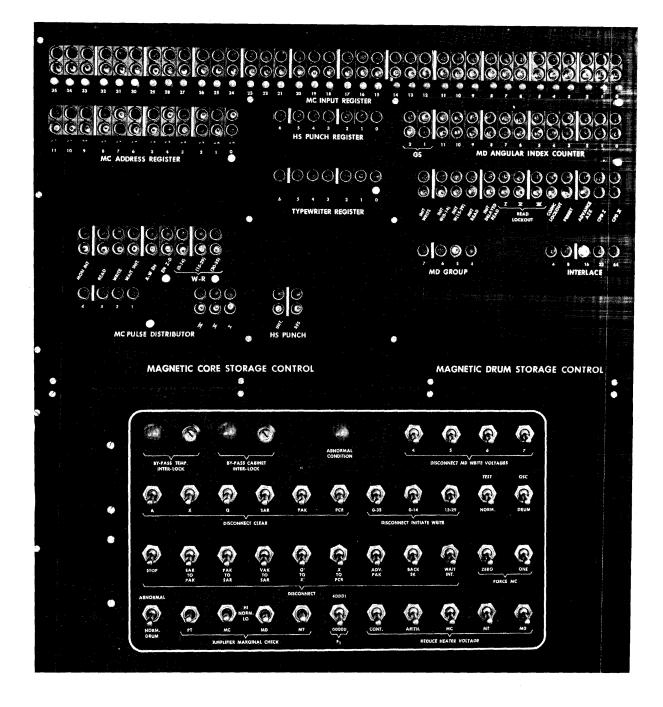

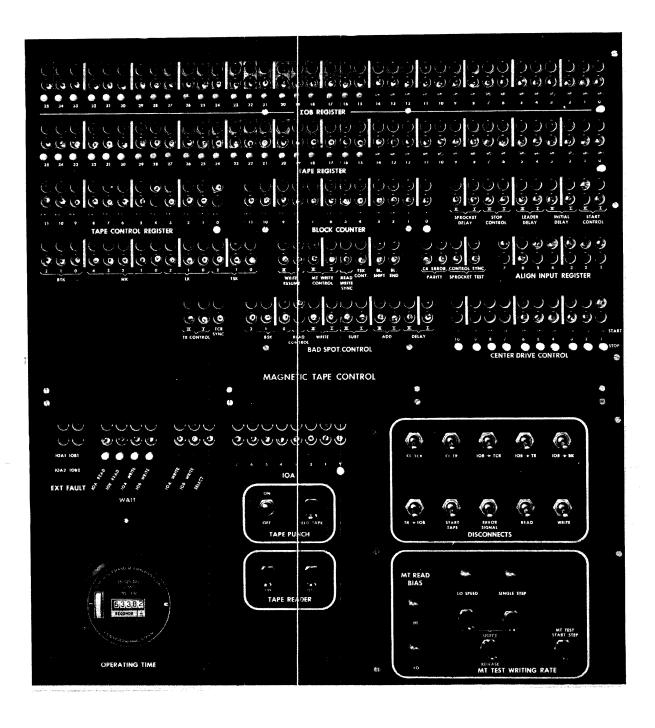

| 1.     | Supervisory Control Panel, Overall View                                              | . 2  |

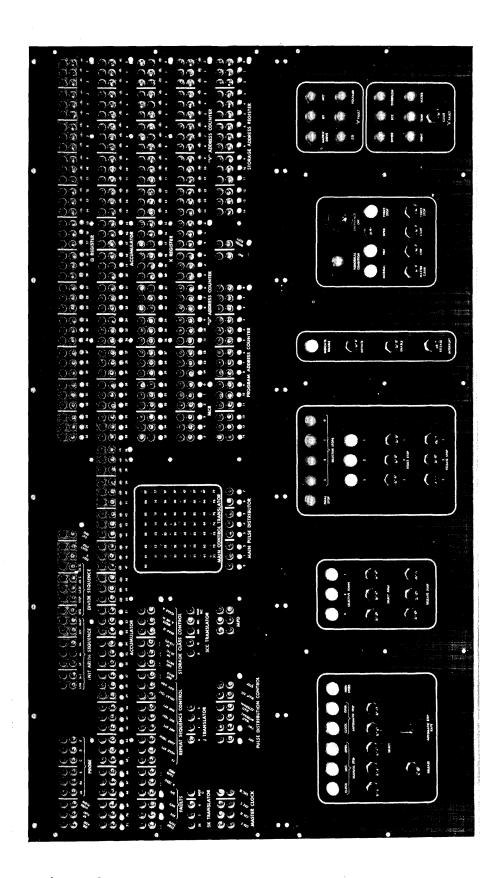

| 2.     | Supervisory Control Panel, Center Section                                            |      |

| 3.     | Supervisory Control Panel, Right Section                                             | 5    |

| 4.     | Supervisory Control Panel, Left Section                                              |      |

| 1.     |                                                                                      | • •  |

| PX 40  | CODING FOR THE COMPUTER                                                              |      |

| 1.     | Programmer's Simplified Block Diagram                                                | . 4  |

#### INTRODUCTION

A computer is a device which is capable of (1) accepting data and instructions to perform operations on this data, (2) executing the specified operations, and (3) producing the results of the operations. More specifically, a general-purpose digital computer is capable of executing the basic arithmetic operations, performing internal data handling operations and logical operations, receiving data from a source external to the computer, and transmitting data to external media of representation. Any problem which can be solved by numerical techniques can be handled and solved by computer operations. The given problem must be analyzed and resolved into a collection of smaller problems, each of which can be solved by the application of the basic computer operations.

A general-purpose digital computer comprises electrical circuits, electronic and magnetic devices, and an associated power supply. Data which is to be manipulated internally is given a numerical representation. Such numbers are represented internally by a state or a condition of a component of the computer. Operations are performed upon the data by applying signals, effecting a change in its condition, to the device which holds the numerically coded data. The function assigned to such a signal is determined according to the change effected in the condition of the component. Data manipulations are performed by an ordered sequence of such impulses upon the components of the computer. The instigation of these impulses, and the regulation of the order in which they are initiated, are the functions of the control portions of a computer.

An operation (permissible to a particular computer) occurs when a portion of control detects a directive to begin the pre-determined sequence of steps necessary to effect the operation. Major directives (computer instructions) are given the computer in a prescribed coded numerical form by the operator of the computer. These directives, and the data which is to be manipulated in a computer operation, may be set aside within the computer, temporarily or for later use, in the <u>storage</u> section. When the information is needed, it is recalled from storage and placed in the appropriate section of the computer. If an arithmetic or logical operation is indicated, data is placed in the <u>arithmetic</u> section of the computer. Here the desired manipulations of the numbers are effected, and temporary storage for results is provided.

The <u>input output</u> portion of the computer consists of the components necessary to (1) provide insertion of coded data and directives into the computer and (2) present externally the results of computations carried out by the computer.

The <u>power</u> system of the computer provides regulated voltages to the four major sections of the computer discussed above.

Discussions of computer systems have led to the establishment of a computer "language". Certain basic terms in this language are discussed subsequently.

- Electronic device which may be in unique states (conditions). STAGE The number of the states possible to the device determines the radix of the number system allowable to representation by the computer. It is possible for a stage in the Univac Scientific to have two unique stable states: a state which is assigned to represent "O", and a state which is assigned to represent "1". Thus, the racix of the number system used in the Univac Scientific is two; the number system is the binary system. A stage may receive as input electrical signals (pulses) which set it to its "1" state, set it to its "0" state, or reverse its present state. Signals derived from the stage indicate the state of the stage and are interpreted as a "l" output or a "O" output. This simple system of input and output to and from a bi-stable stage provides a means of adding, subtracting, and directly complementing binary numbers.

- REGISTER A quantity of stages. The regulation number of stages determines the modulus of the number system allowable to representation by the computer system. The nature of a register allows its use as a storage device for information. Frequently, other storage devices for information are also referred to as "registers".

- ADDRESS A coded number which designates specifically some particular computer register or other internal storage location or device. Information is referenced by its address. Portions of computer control are responsible for directing information to or from an addressed location.

- BIT A binary digit, "O" or "l", represented in the computer by a state of a bi-stable medium of representation.

- WORD Information coded for computer representation as a series of bits. The normal word length is considered to be 36 bits.

- OPERAND A word representing coded data which is involved in computer operations or results from computer operations.

- INSTRUCTION- A 36 bit word which is a coded directive to the control section to initiate and oversee a prescribed sequence of steps necessary to effect a particular arithmetic, logical, or input output operation. Portions of a computer instruction designate the operands which are involved in, and necessary for, the execution of the particular operation.

- OPERATION The coded portion of the instruction which "describes" to CODE computer control which particular operation is to be executed.

- INSTRUCTION- An explanation of what the execution of each instruction FUNCTION accomplishes, with the locations specified of (1) any operands used during this execution and (2) any pertinent results derived from this execution.

- PROGRAM A sequence of coded computer instructions and necessary operands for the solution of a problem.

#### INTRODUCTION

- INPUT OUTPUT systems providing the means of communication between the computer and the operator. Input and output operations involve units of external equipment control, certain of the computer registers, and portions of the computer control section.

- STORAGE consists of devices in which information is set aside for immediate or future use. Each storage location in the Univac Scientific has a unique.address. Each location in the storage section of the computer is an arrangement of 36 bistable elements; hence, each location is capable of storing 36 binary digits.

- ARITHMETIC a section where arithmetical and logical operations are performed and operands and results temporarily stored.

- CONTROL consists of components which direct the operations of the computer.

#### 1. GENERAL

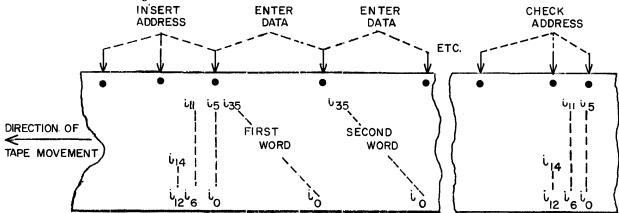

The basic concept of the solution of a problem on a computer is presented in the following paragraphs. First, the computer instructions and their functions must be studied in order to gain a thorough understanding of the capabilities and restrictions of each instruction. When this has been achieved, the problem to be solved is reduced to a sequence of simplified steps, the arithmetic and logical operations of which can be solved by application of the instructions. The Univac Scientific has in its repertoire 41 instructions, each of which is represented by 36 bits,  $i_{35}...i_0$ . The left-most six bits of an instruction, i35...i30, represent its operation code. The remaining 30 bits are grouped as  $i_{29}...i_{15}$  and  $i_{14}...i_{0}$ . These bits are designated as the u address portion and v address portion of the instruction, respectively. These are the portions of the instruction which represent the operands (by referencing their location in storage, for the most part) with which the operation is concerned. A program is prepared by arranging the instructions in the order in which their operations are desired. The instructions are not written in binary but are coded in octal, each octal digit representing three binary digits. Thus, twelve octal digits represent an instruction; two digits represent the operation code; five digits, the u address; and five digits, the v address. For example, the instruction termed "Transmit Positive", whose function is in general "Replace the information at a certain specified location v with the information from another specified location u," is coded abstractly as II uv. With specific locations assigned to u and v, for instance, those with the numerical assignments of 01000 and 00100, the instruction is written in octal as

#### 11 01000 00100.

This represents the binary notation of

####

This instruction, as coded, directs the computer to "replace the content of location 00100 with the content of location 01000".

When the program has been prepared, the coded list of instructions, operands, and any other data comprising it, are prepared for "loading", i.e., entrance into the computer. An input procedure results in the program being stored in the computer at a series of consecutive locations, the first of which must be specified during the input procedure. Each instruction and operand which was coded as a 12 octal digit number is stored at an individual location as a 36 binary digit number. Operands referenced by instructions must be stored at the address specified by the instruction. For instance, the information to be transferred from one location to another by the Transmit Positive instruction, coded as 11 01000 00100, must actually be in storage at the location addressed as 01000. During its execution, a program is usually in storage in a "rapid access" (high speed) type of storage, but it may or may not be placed there initially during the loading process. Rapid access storage allows the fastest possible execution of a program since it provides the quickest acquisition of a word from storage when it is needed.

The order in which the instructions are taken from storage and executed is regulated by the computer control section. Instructions are chosen for execution according to the content of a 15-bit register in the control section. This register holds the storage address of the instruction to be executed. To start the execution of a program, the address of the instruction to be first executed is placed in this register. A controlled series of electrical impulses then (1) "review" the state of the components of the register, determining its content, (2) direct the process of referencing this location, (3) detect the information stored at this address, and (4) transfer it to a 36-bit register in control reserved for holding an instruction during its execution. An instruction remains in this register until it is replaced by the instruction to be executed next. The address of this instruction is again taken from the 15-bit This 15-bit control register has a "counting" facility. address register. Normally, the number represented in the register is advanced by one after each reference to storage is made. This procedure results in the automatic acquisition of instructions for execution from consecutive storage locations.

The presence of the 36 bits of an instruction in the control register reserved for it, authorizes and enables control to direct the execution of the instruction. The particular state of the six left-most stages of the register (those holding the operation code of the instruction) allows a certain sequence of pulses to be released to a portion of the control circuitry. Each pulse in this sequence initiates a series of pre-determined operations. The particular series inaugurated depends upon the combination of bits comprising the operation code. When, during the series of operations, the information at the u or v addressed portion of the instruction is needed, a review occurs of the states of the stages 29 through 15, or 14 through 0, of the register holding the instruction. The process then is to determine this address, reference it, and transfer the data from this location to the register where the data is needed.

All computer operations depend primarily on sequences of pulses originating in the control section. The pulses are issued regularly from a "clock source" at the rate of one every two microseconds. Their release, and the time of their release, to various portions of the control section and to other sections of the computer depends upon the current status of computer operation. This conditional initiation of any sort of a computer operation effects an orderly progression of the steps involved in the execution of an instruction and a series of instructions.

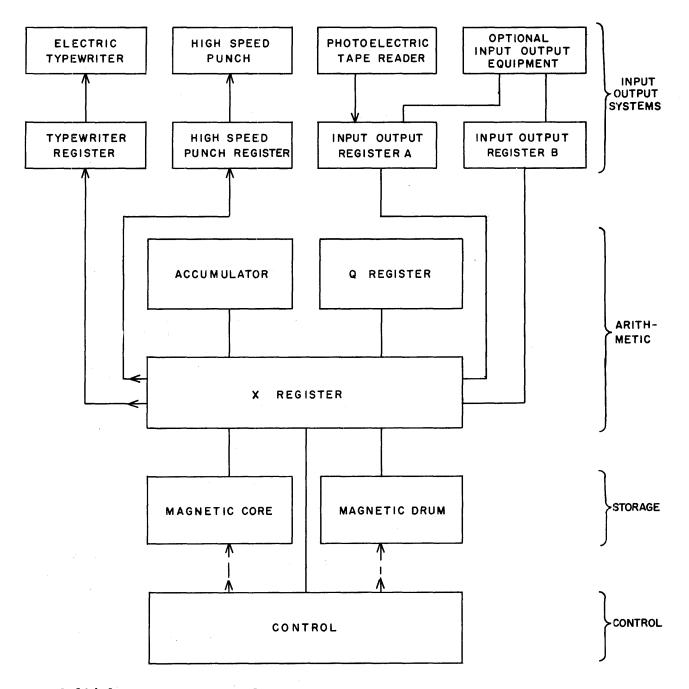

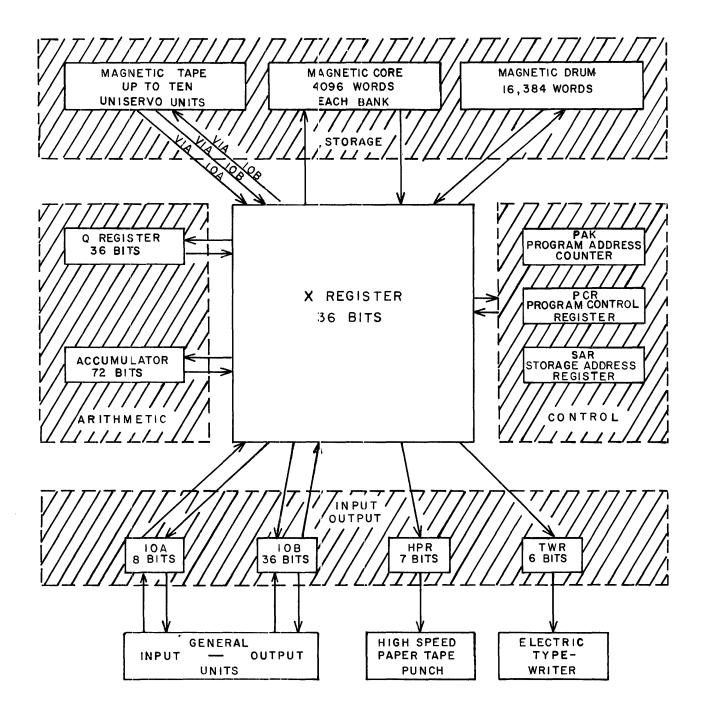

The basic functional make-up of the Univac Scientific General-Purpose Computer System is illustrated in Figure 1 in which the major sections, input output, arithmetic, storage, and control are delineated. A brief discussion of some of the components of the storage, arithmetic, and control sections follows in the subsequent paragraphs. A discussion of the input output systems is found later in the text.

Solid lines connecting blocks indicate the routing of binary information. Dashed lines carry binary information used for storage reference purposes. Information may be routed in both directions unless arrows on a line indicate a one-way transfer.

Lines which carry control signals between the above blocks are not shown on this diagram.

Figure 1.

Simplified Block Diagram of the Univac Scientific General-Purpose Computer System

#### 2. PRINCIPAL REGISTERS

A large quantity of registers, providing static storage of information, is necessary in the computer to facilitate the enumerable computer operations. The number of stages comprising a register depends upon the function that is served by the register. For instance, a register intended to hold a computer instruction consists of 36 stages; a register intended to hold a 15 <u>binary</u> digit address consists of 15 stages. Operations which use in some fashion the content of a register affect all the stages of the register simultaneously. This is described as the "parallel mode" of operation, as opposed to the "serial mode". In the serial mode of operation any sampling, setting, or reversing the states of the stages of a register, proceeds cyclicly one stage at a time.

In addition to the various control registers which are involved in the execution of an instruction, there are three other principal registers which are involved quite frequently. These registers are listed below.

a. X REGISTER. - The X Register is used during the execution of any instruction whose u or v address references an addressable location. The information addressed by u or v is transmitted from its location to the X Register, and from the X Register to the desired position in the computer. Thus the X Register serves as a transmission register for most internal routing of information. In addition the X Register functions as a component of the arithmetic section of the computer. For the corresponding arithmetic register, the X Register holds the addend, subtrahend, multiplicand, and divisor.

In general, the X Register, abbreviated as X, is a 36-stage register capable of temporary storage of 36 bits of information.

b. Q REGISTER. - The Q Register functions as a component of the arithmetic section and also serves as an addressable storage device. The Q Register, designated as Q, comprises 36 stages, affording temporary storage to 36 bits of information.

For the corresponding arithmetic operations, the Q Register holds the multiplier, quotient, and logical multiplier. The Q Register derives its nomenclature from the use of this register for the assembly of the quotient during a divide operation.

The Q Register has "shift left" with "end-around shift" facilities. When a "shift left once" operation is completed, each stage of the register is in the state which was reflected by the stage immediately to the right of it before the operation began. The right-most stage of the register is set to the state of the left-most stage. In other words, the binary digits held in a register are displaced to the left, as many places as is specified by the shift operation, with the leftmost bit being shifted in a circular fashion to the right end of the register.

c. ACCUMULATOR. - The Accumulator functions as a component of the arithmetic section and also serves as an addressable storage device. The Accumulator, referred to by the letter A, comprises 72 stages,

PX 34

4

affording temporary storage to 72 bits of information. Because the Accumulator is capable of holding twice the number of bits of an ordinary storage register, it is often referred to as a "double-length" register. The left-most 36 stages of the Accumulator are referred to collectively as AL; the right-most 36, as AR.

For the corresponding arithmetic operations, the Accumulator holds the sum, difference, product, dividend, and (at the end of a divide operation) remainder. The Accumulator derives its nomenclature from the use of this register for the accumulation of sums. The double length feature of this register allows the formation of sums of more than 36 bits. It also allows the formation of the full product of any two 36 bit numbers, regardless of their numerical value; and conversely, it allows the formation of a quotient whose numerical value is the greatest possible (in absolute value) to represent in a 36-bit register.

The Accumulator also has the "circular shift left" property described for the Q Register. The 72 bits held in the register are displaced to the left, as many places as is specified by the shift operation, with the left-most bit being shifted in a circular fashion to the right end of the register.

The contents of a register, i.e., the bits represented by the states of its stages, is designated by enclosing the symbol for the register in parenthesis. For example, the 36-bit content of the X Register is denoted as (X); the content of the 36 right-hand stages of the Accumulator is denoted as  $(A_R)$ .

#### 3. STORAGE DEVICES

The information which is held in storage consists of instructions which are to be executed and the operands needed by these instructions for their execution. The location of each instruction or operand is referred to as its "address".

a. ADDRESSED STORAGE LOCATIONS. - There are four classes of storage locations which are individually addressed: Magnetic Drum Storage, MD; Magnetic Core Storage System, MCS; the Accumulator, A; and the Q Register, Q. These classes have the following addresses assigned to them:

| Storage Class     | Octal Equivalents<br>of Addresses | Storage Space:<br>Number of Words |

|-------------------|-----------------------------------|-----------------------------------|

|                   |                                   |                                   |

| MCS-O             | 00000-07777                       | 4096                              |

| MCS-1             | 10000-17777                       | 4096 optional                     |

| MCS-2             | 20000-27777                       | 4096 optional                     |

| Illegal Addresses | 30000-30777                       | -                                 |

| Q                 | 31000-31777                       | 1                                 |

| Ā                 | 32000-37777                       | l double length                   |

| MD (Group 4)      | 40000-47777                       | 4096                              |

| MD (Group 5)      | 50000-57777                       | 4096                              |

| MD (Group 6)      | 60000-67777                       | 4096                              |

| MD (Group 7)      | 70000-77777                       | 4096                              |

|                   |                                   |                                   |

The banks of Magnetic Core Storage, MCS-1 and MCS-2, are optional to the computer system. If this storage is not provided, the addresses assigned to MCS-1 and/or MCS-2 are illegal addresses.

Additional storage, in which the information is not individually addressed, is provided by up to ten Uniservo magnetic tape units.

Information is acquired from storage in MCS, MD, A, or Q by first determining the storage class of the address of the instruction or operand desired. Following this, the address is transmitted to the locating control of the proper storage class where the specific storage location is found (if the storage class is MC or MD). Then the information at this location is transmitted to the X Register. Operations of this kind are referred to as "reading" operations. "Writing" operations, or the transfer of information to a storage location, are accomplished in a similar manner with the information in the X Register being placed at a storage address as located by the control circuitry.

b. MAGNETIC DRUM STORAGE SYSTEM (MD). - The Magnetic Drum Storage System provides medium-access binary storage. Digital information is stored in the form of magnetized areas on the surface of a continuously rotating cylinder called a magnetic drum. The medium of storage is a magnetized bipole having either of two polarity orientations in the lateral (or peripheral) direction. For all practical purposes, information recorded on the drum is stored permanently. It may, however, be removed by special erase techniques, or it may be replaced by simply writing new information over it. Reading from the drum does not in any way alter the contents of the location read.

Each individual storage location is identified by specifying its angular and axial coordinates on the drum surface. The 36 bits of a word are stored at 36 individual axial positions on the drum. A drum group has angular storage space available in normal drum operation for 4096 36-bit words. A total of four drum groups results in an MD storage capacity of 16,384 words. When a word or a portion of a word is to be transmitted to or from the magnetic drum, all the bits to be transmitted are handled simultaneously, i.e., in parallel. Information may be recorded or read in any given area only once during each drum revolution, resulting in a maximum access time of 34 milliseconds.

The first octal digit of an MD address (4, 5, 6, or 7) specifies the drum group or axial location of a word. The remaining four octal digits specify the angular address (0 through 7777 octal) of the word in the designated group. The angular locations during a revolution of the drum are counted and recorded by the Angular Index Counter. An MD reference made during a computer operation is translated according to a chosen "interlace", and held in an address interlace chassis. When coincidence is detected between these two MD addresses, the reading or writing operation occurs. According to the pre-selected interlace, the reading or writing occurs at a regulated interval from the actual drum location originally referenced. Interlaces of 4, 8, 16, 32, or 64 are available. The address held in the address interlace chassis is the modular product (in binary) of the angular portion of the MD address referenced, and the power of two specified by the interlace. If an interlace of four is chosen, coincidence occurs between consecutive MD references and the address of every fourth MD location, etc. For example, if an interlace of eight is chosen, an MD reference listed below in the left-hand column results in the selection of the MD location

| listed | below | in   | the  | right-hand | column. |

|--------|-------|------|------|------------|---------|

| TTDCCC | DCTON | T 11 | DITO | Light hund | oorumn. |

| Original Reference | As held in the<br>Address Interlace Chassis |

|--------------------|---------------------------------------------|

| 40000<br>40001     | 40000<br>40010                              |

| 40001<br>40002     | 40010                                       |

| •                  | •                                           |

| 40777              | 47770                                       |

| 41000<br>41001     | 40001<br>40011                              |

| •                  | •                                           |

| 41777              | 47771                                       |

| •                  | •                                           |

| 47000<br>47001     | 40007<br>40017                              |

| •                  | •                                           |

| 47777              | 47777                                       |

The variable interlace system allows the selection of the minimum computer time for consecutive MD read and write operations. The time required for one drum revolution is 34 milliseconds. Thus, the time which elapses between the positioning of physically adjacent drum locations for read or write operations is approximately eight microseconds. An interlace of "1" would mean that references to two consecutive MD addresses would have to be made in less than eight microseconds for the drum to be properly positioned for the second read or write operation before a complete drum revolution has ensued. If the references are made in less than 32 microseconds, a four interlace effects the minimum time possible for the MD read or write operations. The interlace which is in effect is indicated by an illuminated light on the upper right section of the Supervisory Control Panel of the computer.

The preceding paragraphs were written with the normally addressable MD storage locations in mind. Each drum group has, in addition to the previously mentioned 4096 locations for storage, a "reserve space" of 160 locations which are not normally addressable. Communication is established with these locations, and broken with the rest of the drum locations, by setting the NORMAL/ABNORMAL DRUM switch on the lower right section of the Supervisory Control Panel to ABNORMAL. This will allow the detection of coincidence with reserve space locations zero through 0237 (octal). When the normally addressed portion of the drum is in position for reading or writing, the Angular Index Counter counts from zero to 7777 (octal) but no coincidence tests are made. When the reserve

space on the drum is in position for reading or writing, the Angular Index Counter counts from zero to 0237 (octal) and checks for coincidence with addresses in the address interlace chassis. The MD references made for Abnormal drum reading or writing must be properly coded so that their form in the interlace chassis will be octal -0000 through -0237. (The first octal digit may be 4, 5, 6, or 7 depending up on the drum group to be addressed.)

c. MAGNETIC CORE STORAGE SYSTEM (MCS). - Each bank of the Magnetic Core Storage System provides rapid-access storage for 4096 36-bit words. Each core is a bistable element capable of storing a "1" or a "0", dependent upon the direction of magnetization of the core. The cores are arranged in a 64 x 64 matrix with 36 such matrices. The 36 digits of a given word are represented by the state of 36 corresponding cores, one in each of the 36 matrices. Reading and writing operations of a word, or portion of a word, are performed in a parallel mode with a simultaneous transmission of bits. Certain sequences of pulses on wires through the cores, producing magnetizing forces of a certain polarity, are used to perform the reading and writing operations. Reading from MC does not in any way alter the contents of the location read.

Magnetic Core Storage is non-volatile; comparable to non-volatile storage in the Magnetic Drum Storage System.

d. A AND Q AS STORAGE MEDIA. - The Accumulator and Q Register are available as temporary storage registers since they may be addressed. The Q Register is normally addressed as octal 31000 although any of the addresses 31000-31777 are permissible. Similarly, the Accumulator is normally addressed as 32000 with the addresses 32000-37777 being permissible.

#### 4. CONTROL COMPONENTS.

Each of the function groupings of the computer, input and output, storage, and arithmetic, has individual control systems which direct the operations of the section under their influence. These control systems are in turn directed in their operations by the main computer control. This overall influence exerted by computer control is necessary for time-wise reasons: an established sequence of internal actions is essential for the processing of any coded information. The computer control initiates and superintends these patterns of actions during their performance.

The main control section receives the instructions which the computer is to carry out; it interprets them, and directs their execution with the operands specified. The computer must be manually started, but can be either automatically or manually stopped. (In addition to being automatically controlled by a program of instructions, the computer can be manually controlled from the Supervisory Control Panel which contains all the necessary controls and indicators for manually operating the equipment.)

The principal components of the control section are as follows.

a. PROGRAM ADDRESS COUNTER. - The Program Address Counter, PAK, is a 15stage additive register. During computation PAK generates the consecutive addresses of the programmed instructions to be executed. The address in PAK is normally referred to each time an instruction word is to be obtained from the computer memory. The starting address for a computation may be manually inserted into PAK before the START (operation) button is pushed. If this is done, computation will begin by picking up the instruction stored at that address. If PAK is not manually pre-set, it will automatically be set to MD address 40000. During the normal termination of an instruction, the next instruction to be executed (the address of which is held at that time in PAK) is extracted from storage; and the content of PAK is advanced by one. Thus, during the termination of the instruction at address y, the instruction at y + 1 (the address held in PAK) is extracted from storage, and PAK is advanced to y + 2. If the instruction at address y indicated that the sequential acquisition of instructions be disrupted by a jump to an instruction not stored at a consecutive address, this instruction's address is inserted into PAK previous to the termination operations.

The program interrupt feature of the Univac Scientific, discussed in a later paragraph, interrupts the normal process of acquiring the address of the next instruction from PAK.

The generation of consecutive binary numbers in PAK is restricted by the following conditions in its physical structure. There is no communication between the stages  $PAK_{12}$  and  $PAK_{11}$  unless the stage  $PAK_{14}$  contains a value of one. Thus, PAK<sub>12</sub> will not be affected by the advance of PAK after the contents of PAK<sub>11</sub> ... PA $\bar{k_0}$  reach the value of  $2^{12}$ -1 (7777 octal). The next advance of PAK, after such a value is reached, results in the contents of the stages PAK11 ... PAKO being changed to zeroes. If PAK14 does contain a one, the contents of PAK may be increased until the contents of PAK13 ... PAKO reach the value of  $2^{14}$ -1. Then, since there is no communication between the stages PAK13 ... PAKO being changed to zeros with the value of one being left undisturbed in PAK14. This "closed loop" system effects the generation of successive MCS addresses in PAK as follows: the addresses of each bank of MC can be advanced to (octal) -7777, with the next advance of PAK resulting in its contents becoming (octal) -0000. If any of the Magnetic Drum addresses, regardless of the group, are represented in PAK, the addresses can be generated consecutively to 77777 with the next advance of PAK resulting in its contents becoming 40000.

b. PROGRAM CONTROL REGISTERS. - The Program Control Registers, PCR, receive each instruction and temporarily store it during its execution. The registers consist of the Main Control Register, MCR, the U Address Counter, UAK, and the V Address Counter, VAK. Each instruction sent to PCR consists of a 6-bit operation code which is stored in MCR, a 15-bit u address portion which is stored in UAK, and a 15-bit v address portion which is stored in VAK. Each instruction is obtained from some 36-bit storage location as specified by the Program Address Counter, PAK. The physical structures of UAK and VAK are similar to that of PAK. An additional restriction on the generation of consecutive binary numbers in UAK and VAK is as follows. If an A or Q address is in UAK or VAK, it is not possible to advance the content of the stages zero through eight of UAK or VAK beyond  $2^9$ -1 (octal 777). Thus, A or Q addresses are generated from octal 32000 to 32777 to 32000 and from octal 31000 to 31777 to 31000, respectively. The generation of consecutive MC and MD addresses is the same as in PAK.

c. MASTER CLOCK. - All the activities which take place within the computer, except for certain ones in the output sections, are synchronized by a central

timing system, called the Master Clock. During NORMAL computer operation, the clock generates 500 kc clock pulses based on timing pulses from the Magnetic Drum Storage System, and after exerting certain controlling influences over them, supplies them to circuits throughout the computer. During TEST operations, a 500 kc oscillator may be used instead of the drum as the basic source of timing pulses.

d. MAIN PULSE DISTRIBUTOR. - The Main Pulse Distributor, MPD, receives clock pulses and distributes them in sequences of from four to eight pulses to the Command Timing Circuits. The distributor supplies each of the pulses sequentially on its eight output lines. In an eight pulse cycle, all of the output lines are used, and the pulses are designated, in the order of their generation, MPO through MP7. The selection of a particular cycle is made on the basis of the operation code held in the Main Control Register, MCR. Each code selects the sequence which will permit the performance of the generation in the least possible time.

e. MAIN CONTROL TRANSLATOR. - The principal translator of the Main Control Translator, MCT, receives a 6-bit operation code from the Main Control Register and produces accordingly a single operation code "enable". In the Command Timing Circuits, the enable from MCT is used in the selection of the sequence of commands which are needed to execute the instruction currently in the Main Control Register. In the Main Pulse Distributor, the MCT enable is used in the selection of the sequence of the sequence of main pulses required for the operation.

f. COMMAND TIMING CIRCUITS. - The Command Timing Circuits, CTC, produce a discrete sequence of commands which execute the specified operation. The commands initiated are chosen by combining the operation code enable from the Main Control Translator and the pulse cycle received from the Main Pulse Distributor. A pulse cycle consists of two or more of the pulses MPO through MP5, and MP6 and MP7. It initiates the commands which execute the operation on pulses MPO through MP5; reads the instruction to be executed next from storage into the X Register on MP6; then transfers the instruction from X to PCR on MP7.

g. PROGRAM INTERRUPT CONTROL. - An interrupt selection interferes with the execution of the normal termination commands occurring on MP6. The normal termination commands take the address of the next instruction to be executed from PAK and then advance PAK. With the interrupt in effect, the address 00002 in Rapid Access Storage, F3, is chosen as the address of the next instruction to be executed. This instruction is read from storage to the X Register. On MP7 the normal transfer of the content of X to PCR is made. This puts the instruction at F3 in position for execution and leaves the address in PAK undisturbed. Thus, for example, if the interrupt becomes effective during the execution of an instruction at address y, the address y + 1 in PAK (or u or v if the instruction being executed calls for a jump) is undisturbed during MP6, and (F3) is taken as the next instruction. By appropriate programming, the content of PAK may be inserted in a temporary storage location and later referred to in such a way as to return operation to the instruction stored at the address in PAK.

The selection of an interrupt is effective only on an MP6 generated during the normal termination commands. This means that the selection of an interrupt during the repeated execution of an instruction is not effective until the

repeating is brought to a conclusion, either by the execution of the instruction n times or by the occurrence of a jump. (This is discussed in more detail under the Repeat instruction, Sequential Presentation of Instructions section.) The interrupt selection may be made manually from the Supervisory Control Panel or as a function of input output operations. Selecting an interrupt option during input output operations is discussed later in the Input Output section. Briefly, an interrupt selection may be made for input output operations by appropriate programming or a manual setting on the piece of external equipment involved.

#### 5. REPRESENTATION OF NUMERICAL VALUES

The bi-stable characteristic of the elements of the computer dictates the use of binary number notation in the representation of information. However, the computer cannot determine whether an array of bits is an instruction, data with numerical value, or data coded in some arbitrary fashion. If an array of digits is confronted in a register normally reserved for holding an instruction, the computer will try to treat it as an instruction; if an array of bits is confronted in an arithmetic operation, the computer will deal with it as having numerical value.

The computer treatment of an array of bits in arithmetic operations assumes the assignment of a numerical value to the bits as follows: the left-most bit of an array determines the sign of the number; a "1" designates a negative value; a "0" designates a positive value. The remaining bits of the array determine the absolute value of the number.

One's complement notation is used for expressing the negative of a quantity. The one's complement of a binary digit is the digit subtracted from the value of one. The one's complement of a digit represented by the state of a bi-stable element is formed by merely reversing the state of the element. In a number system which includes all the possible combinations of "O's" and "I's" from 000 ... 000 to 111 ... 111, positive quantities are represented by the combinations in which the left-most bit is zero, 000 ... 000 to 011 ... 111. The negatives of these quantities are represented by their one's complement, the combinations in which the left-most bit is one, 111 ... 111 to 100 ... 000. This left-most bit is termed the sign-bit of the number.

The bits representing a number are held in an arrangement of bi-stable elements, such as the stages of a register. The designation of the left-most element of k elements is given the subscript k-1; the designation of the adjacent element is given the subscript k-2; and continuing to the right, the designation of the right-most element is given the subscript 0. For example, the 36 stages of the Q Register are designated as  $Q_{35}$ ,  $Q_{34}$ , ...,  $Q_1$ ,  $Q_0$ . In general, the stage  $S_{k-1}$  of a k stage register holds the sign bit of a number, and the absolute value of the number is determined by the contents of stages  $S_{k-2}, \ldots, S_0$ . If the sign bit is "0", the bits in stages  $S_{k-2}, \ldots, S_0$  are the coefficients a of a binary number  $a_{k-2}2k-2 + a_{k-3}2k-3 + \ldots a_12^1 + a_02^0$ . If the sign bit is "1", the one's complement of the bits in stages  $S_{k-2}, \ldots, S_0$  are the coefficients of the absolute value of the number. (The term "most significant bit" is given to the first digit from the left which differs from the digits to its left.) The values possible to represent in k bi-stable elements are in the range with the limits of  $\pm (2k-1-1)$ , inclusive. In a

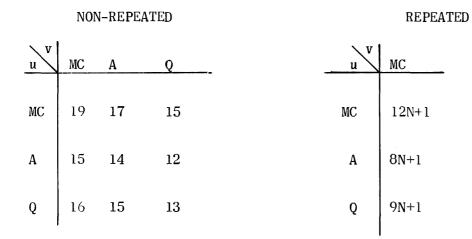

36 stage register, the limits are  $\pm (2^{35}-1)$ ; in the 72-stage Accumulator, the limits are  $\pm (2^{71}-1)$ . The modulus of a number system represented by k stages is  $2^{k}$ . However, if "plus zero" and "minus zero" are treated as a unique quantity, as is the case in the Univac Scientific, the modulus is  $2^{k}-1$ .