## governmentattic.org

"Rummaging in the government's attic"

Description of document: Department of Defense history: <u>History of NSA</u>

[National Security Agency] General-Purpose Electronic

**Digital Computers**, Samuel S. Snyder, 1964

Requested date: June 2009

Released date: June 2009

Posted date: 17-May-2010

Title of document History of NSA General-Purpose Electronic Digital

Computers

Date/date range of document: Addresses computer systems prior to 01-January-1964

Source of document: National Security Agency

Declassification Services (DJ5)

Suite 6884, Bldg. SAB2 9800 Savage Road

Ft. George G. Meade, MD, 20755-6884

Note: Originally released under NSA FOIA 41023, 2/9/2004

Requested and re-released under Mandatory

Declassification Review in June 2009

The governmentattic.org web site ("the site") is noncommercial and free to the public. The site and materials made available on the site, such as this file, are for reference only. The governmentattic.org web site and its principals have made every effort to make this information as complete and as accurate as possible, however, there may be mistakes and omissions, both typographical and in content. The governmentattic.org web site and its principals shall have neither liability nor responsibility to any person or entity with respect to any loss or damage caused, or alleged to have been caused, directly or indirectly, by the information provided on the governmentattic.org web site or in this file. The public records published on the site were obtained from government agencies using proper legal channels. Each document is identified as to the source. Any concerns about the contents of the site should be directed to the agency originating the document in question. GovernmentAttic.org is not responsible for the contents of documents published on the website.

# HISTORY OF NSA GENERAL-PURPOSE ELECTRONIC DIGITAL COMPUTERS

1964

Approved for Release by NSA or 02-09-2004, FOIA Case #41023

Regraded to FOR OFFICIAL USE ONLY

Declassification Officer

C:-

Date: 1/-18-7

## HISTORY OF NSA GENERAL-PURPOSE ELECTRONIC DIGITAL COMPUTERS

By Samuel S. Snyder

1964

Department of Defense Washington, D. C. 20301

#### **PREFACE**

ř.

The author has attempted to write this material so that it will be easily understood by those who have had only limited experience with computers. To aid those readers, several terms and concepts have been defined, and Chapter 1 includes a brief discussion of principles of computer operation, programming, data-preparation problems, and automatic programming. Engineering terminology has been held to a minimum, and the history of programmer training, personnel and organizational growth, and the like has not been treated. To some small extent, the comments on operational utility bring out the very real usefulness of computers for the solution of data-processing problems.

The cutoff date for events related here was the end of December 1963.

S.S.S.

## TABLE OF CONTENTS

### CHAPTER 1 -- BACKGROUND

| Description                                              | Page                                                                                         |

|----------------------------------------------------------|----------------------------------------------------------------------------------------------|

| Punched Card Equipment and the Computer Computers in NSA | - 4<br>- 4                                                                                   |

| CHAPTER 2 AGENCY-SPONSORED COMPUTERS                     |                                                                                              |

| ATLAS I and ABEL                                         | - 14<br>- 29<br>- 31<br>- 36<br>- 36<br>- 36<br>- 46<br>- 55<br>- 59<br>- 59<br>- 59<br>- 60 |

| International Business Machines Corporation IBM-701      | - 65<br>- 66<br>- 67<br>- 67                                                                 |

| IBM-1410                                                 | - 71<br>- 76                                                                                 |

## TABLE OF CONTENTS

## (CONTINUED)

| Description                                                                             | age                        |

|-----------------------------------------------------------------------------------------|----------------------------|

| General Precision, Inc                                                                  | 76<br>76<br>78<br>78<br>82 |

| CHAPTER 4 REMOTE-OPERATED COMPUTERS                                                     |                            |

| ROGUE (ALWAC IIIE)                                                                      | 85<br>88<br>89             |

| APPENDIX                                                                                |                            |

|                                                                                         | 97<br>98                   |

| References                                                                              | 99                         |

| ILLUSTRATIONS                                                                           |                            |

| Figure Description F                                                                    | age                        |

| <pre>Block Diagram of Digital Computer Typical Problem Flow Chart ATLAS I Console</pre> | 3<br>5<br>9                |

|                                                                                         | 11<br>15<br>15<br>16       |

| 10 ABNER (1) Memory Cabinet                                                             | 20<br>24<br>25             |

## Illustrations (continued)

| Figure   | Description                                                       | Page        |

|----------|-------------------------------------------------------------------|-------------|

| 15       | BAKER                                                             | - 26        |

| 16       | SOLO                                                              |             |

| 17       | BOGART Console, with IBM 727 Tape Drives                          | - 34        |

| 18       | BOCART Serial ?                                                   | - 35        |

| 19       | CUB                                                               | - 37        |

| 20       | Partial View of CRISPI, Showing Paper-Tap                         | e           |

|          | Input, UNIVAC 1224A, and "B" Console                              | - 37        |

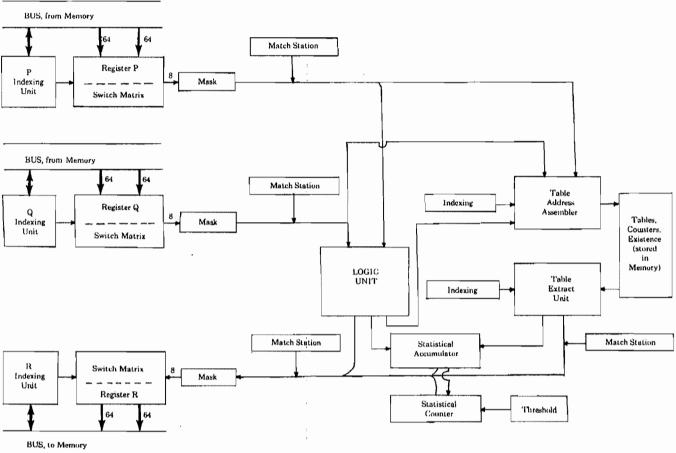

| 21       | Input, UNIVAC 1224A, and "B" Console HARVEST System Block Diagram | - 44        |

| 22       | HARVEST Operator's Console, Showing IBM                           |             |

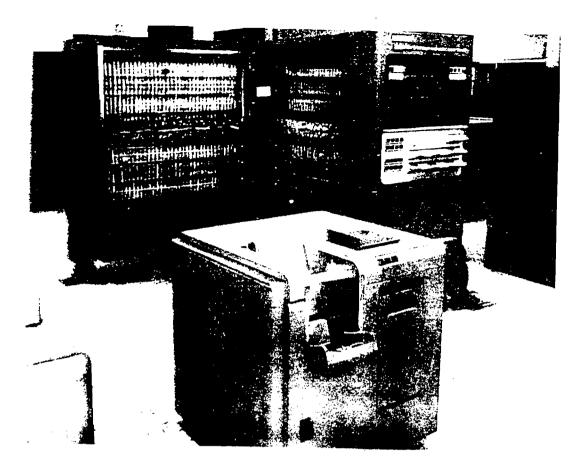

|          | 1403 Line Printer, Right Background                               | - 47        |

| 23       | HARVEST Operating Area, General View,                             |             |

|          | Showing TRACTOR in Left Background                                |             |

| 24       | HARVEST Maintenance and Engineering Con-                          |             |

|          | soles: Arithmetic and Logic Unit (left)                           |             |

|          | Streaming Unit (right)                                            |             |

| 25       | HARVEST The 16 Frames of the Central                              |             |

|          | Processing Unit                                                   | - 50        |

| 26       | HARVEST Tape Control Units and Tape Drive                         | s 51        |

| 27       | HARVEST The 6 Large Memories                                      | - 52        |

| 28       | HARVEST One Unit of the Fast Memory -                             | - 53        |

| 29       | HARVEST TRACTOR Cartridge Handler                                 |             |

| 30       | HARVEST Streaming Data Paths                                      | - 56        |

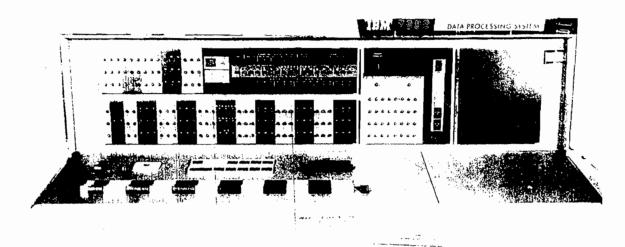

| 31       | IBM-705, Showing SINBAD Control Panel at                          |             |

|          | Right of 705 Console IBM-705 Core Memory                          | - 68        |

| 32       | IBM-705 Core Memory                                               | - 69        |

| 33       | IBM-704                                                           | - 70        |

| 34       | IBM-704 Core Memory                                               | - 70        |

| 35       | IBM-650 General View                                              | - 72        |

| 36       | IBM-650 Console                                                   | - 72        |

| 37       | IBM-650 Disk Storage                                              | - 73        |

| 38       | IBM-650 Inquiry Station                                           | - 74        |

| 39       | IBM-1401                                                          | - 75        |

| 40       | LGP-30                                                            | - 77        |

| 41       | WELCHER                                                           | - 79        |

| 42<br>43 | CDC-1604                                                          | - 80        |

| 43<br>44 | CDU-1604                                                          | - 8T        |

| 44<br>45 | Control Data 160-A Computer ALWAC IIIE                            | - 83        |

| 45<br>46 | ROB ROY Outstation                                                | - 8/        |

| 40       | ROB ROY Control Panel                                             | - 50        |

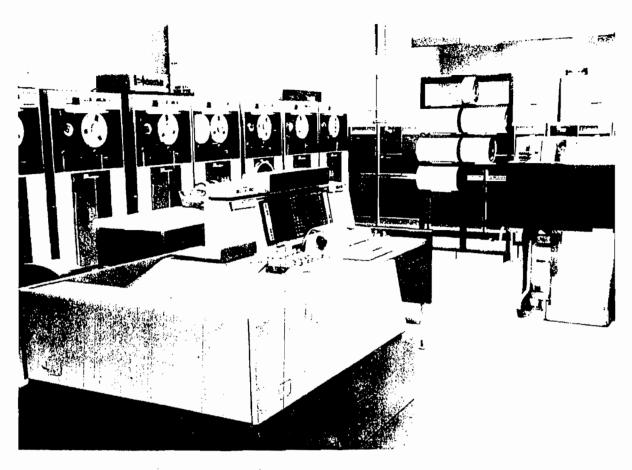

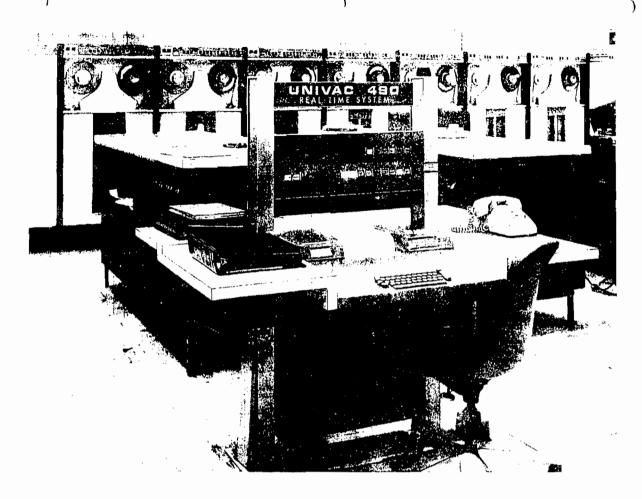

| 48       | UNIVAC 490 (RYE) General View                                     | - 90        |

| 40       | UNIVAC 490 (KYE) GENERAL VIEW                                     | <b>-</b> 71 |

## CHAPTER 1 BACKGROUND

Most writers on digital computer development tend to start with discussions of the abacus and continue with Charles Babbage's Analytic Engine, the desk calculator, and the big relay calculators of Bell Laboratories and Harvard. Indeed, the development of computing machinery did follow such a path. But the role of computers at NSA can be better appreciated when considered from the viewpoint of application.

Punched Card Equipment and the Computer

The extraordinary versatility and efficiency of electronic Computers have made them useful in handling almost every class of data-processing and analytic problem. From this point of view and in this respect, at NSA, punched-card equipment — keypunch, reproducer, sorter, collator, and tabulator — could be called the forerunners of the electronic computer.

For the 15 years beginning about 1935, NSA's predecessors used punched-card equipment to attack wider and wider ranges of problems. During this time many special-purpose machines were also built, including some designed as attachments to punched-card equipment. The use of punched-card equipments as general-purpose tools continued to grow until, by the end of World War II, 750 machines had been installed.

Punched-card equipment -- keypunch, reproducer, sorter, collator, and tabulator -- were the forerunners of the electronic computer in every respect excepting speed and automatic operation. This is true because of the use of the punched-card as a unit record, flexibility of plugboard together with switching capabilities in each machine, and versatility inherent in successive card passes through different equipments. The following types of data analyses could be done using punched-card equipments:

expanding, reproducing (Reproducer) distributing, sorting (Sorter) merging, selecting (Collator) counting, printing (Tabulator)

The general-purpose computer logically corresponds to punched-card equipment in that a variety of elementary operations (the order code) can be combined in a variety of ways

(the programs) and applied to unit records (data stored in specific memory locations). The versatility is further increased by treating the program steps (instructions) as data themselves and eliminating the necessity for manual operations between successive logical operations. Finally, the great difference in speed made possible by electronic circuitry in the large computers has virtually eliminated the punched-card approach as our principal general-purpose tool.

#### Computers in NSA

with the earliest design work on computers, in 1946, came the realization of the potential usefulness of such machines for Agency purposes. Quite probably this Agency's predecessors were the first to develop sophisticated analytic applications of such machines. This story is detailed later in the discussions of ATLAS I and ABNER. The use of computers by NSA has increased considerably, beginning with one of the first machines in the country, installed in December 1950.

NSA's computer installation probably ranks among the largest in the country. The chronological listing (Table 1, page 93) shows these acquisitions in the order of their installation and includes references to the page in the text where each computer is discussed.

#### Computer Principles

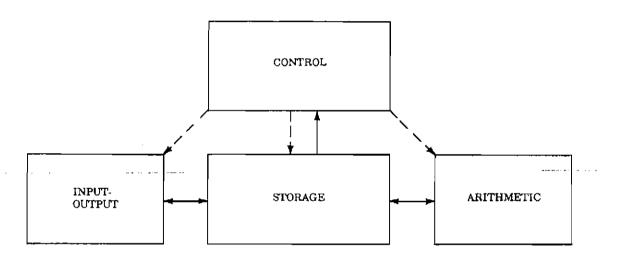

Most modern electronic digital computers, beginning with the successors to the famous ENIAC, have been composed of four principal units: input-output, storage, arithmetic, and control (fig. 1). Data and instructions, prepared in advance on some machine-readable medium (punched cards, tape, and the like), are fed into the machine system, and the data is operated on automatically, according to the steps specified in the instructions. Such instructions are stored in the same internal storage medium as the problem data but are interpreted by the control unit. An "instruction" normally indicates: (1) the operation to be performed by the arithmetic unit, (2) the location in storage (its address) of one or more operands, and (3) the address of the result of the operation. of the reasons for the great flexibility of the modern computer is its ability to modify its own instructions or the course of problem solution, depending upon intermediate results. A variation of this capability is the technique of causing the incoming data-stream characters themselves to form addresses for insertion in skeleton instructions later to be executed.

\_\_\_\_\_ Data Paths

Figure 1.—Block Diagram of Digital Computer

#### Programming Principles

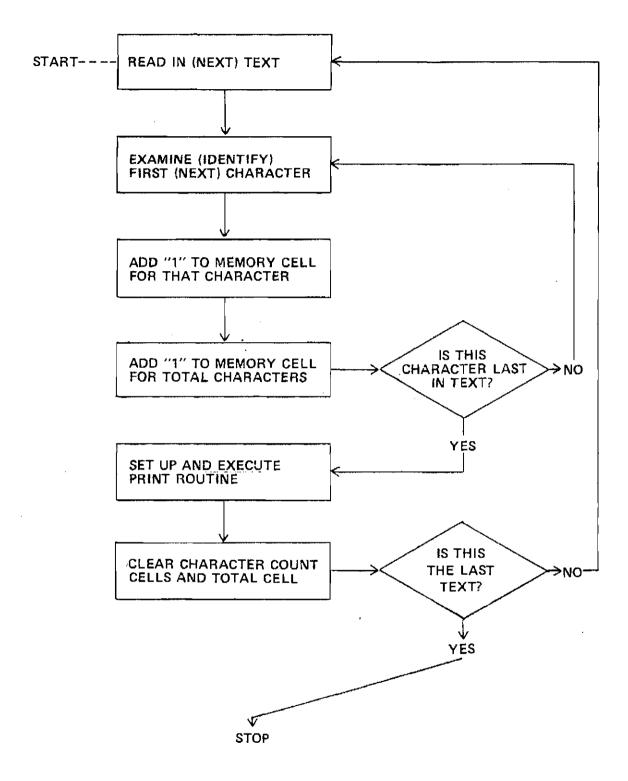

Any analytic or data-processing requirement, however complex, can be logically reduced to a succession of elementary operations that follow from binary decision-points (yesor-no choices), provided knowledge exists of a logical method of attack. A flow chart (fig. 2) for a sample problem shows the use of such dichotomous, or two-choice, logic to break a complex problem into the major steps that will lead to possible solution. In similar fashion, each of such major steps is susceptible to further breakdown into smaller, more detailed, steps, and so on down to the individual elementary machine operations that are the smallest logical unit and that correspond to the individual computer instructions.

#### Data Preparation

An important and essential aspect of the use of any data processing machines is the initial step -- the preparation of data for input. In connection with the general-purpose use of punched-card equipment, the key-punch has been mentioned as providing means of transforming information into a form that can be read by other machines. The key-punch perforates cards in specific positions to represent data under study. Punched paper tape is also used as machine input and is usually punched in 5- or 7-level codes. Recently the use of magnetic tape has increased, although it must usually be prepared from punched cards or tape. Two points should be emphasized:

- 1. Our method for going from hard copy to machine-readable mediums has not improved -- a small army of key-punchers and paper-tape punchers is still employed.

- 2. The existence of several media, here and in the field, requires the use of large quantities of equipment and time just to convert from one medium to another (frequently several times within one job). Many machines, including several general-purpose computers, have been built for the sole purpose of data conversion and rearrangement.

#### Automatic Programming

In the preceding brief description of the principal parts of the typical computer and of organizing a problem for computer attack, the necessity for a breakdown into elementary operations was pointed out. Most of these elementary operations are more detailed -- require much finer attention -- than people are accustomed to. When a workable program

FIGURE 2. TYPICAL PROBLEM FLOW CHART -- FREQUENCY DISTRIBUTION OF ALPHABETIC TEXT

(or routine or subroutine, as smaller subdivisions are called) is completed, it is natural to try to avoid the necessity of repeating the whole operation the next time this particular function is required. As a result, routines of standard functions are commonly stored in "libraries," and special programs, called "compilers," perform the function of combining several such routines and adjusting addresses for varying conditions. To facilitate the writing of machine-language instructions, the instruction codes of many computers use mnemonics that must later be converted into the individual computer words. Programs for performing this conversion automatically are called "assemblers." Higher forms of languages have been developed that use a combination of rigorous English and mathematical notation to express functions and parameters of problems and thus release the analyst/ programmer from becoming a full-time machine specialist. grams for transforming these higher languages are called "translators; " they generate actual computer programs ready to execute a problem solution. Special programs for regulating overall computer operations, keeping records, monitoring various types of simultaneous operations, and for many other purposes are called "supervisors" or "executive" routines. In the past, programmers in NSA have been less inclined to use these techniques than computer users in other fields, primarily because commercially developed systems have been unsuited to the specialized nature of Agency operations. More recently, however, such techniques have become the rule, and the great ALPHA language-development effort required for HAR-VEST, for example, will certainly have a far-reaching effect on future large systems.

#### Special-Purpose Attachments

In large-scale equipment planning, more and more use is being made of the combination of several kinds of equipment into single operating complexes. Actually, this procedure parallels what was done many years ago when attachments were built to function with the IBM Tabulator. In 1954 the FARMER proposal first suggested the idea of special attachments to a computer, and the design of HARVEST made specific provision for the attachment of external function devices. The currently popular application of this principle is the designing of highly efficient counting, comparing, or other processing devices for attachment to a general-purpose computer for use in sophisticated attacks on complicated problems to achieve greater efficiency than would be possible using the computer alone.

Impact of NSA on Commercial Computer Developments

In addition to contracts for computer purchase or lease and the development of engineering techniques, the primary

influence of NSA on industry has been felt in those instances where technical leadership or management foresight has influenced or led directly to industrial computer pioneering. A few examples follow.

First, the sponsorship of the ATLAS I by NSA's Navy predecessor led directly to placing Engineering Research Associates on a firm footing as one of the country's pioneering computer firms. ERA's commercial 1101 and 1103 computers were almost identical to ATLAS I and ATLAS II respectively. With the merger of ERA and the Eckert-Mauchly Corporation into the Remington-Rand-UNIVAC organization, the 1101 and 1103 became a part of the UNIVAC line. Through the National Bureau of Standards, NSA's Army predecessor contracted for the construction of a mercury delay line memory for ABNER. Technitrol Corporation not only built memories for ABNER and the National Bureau of Standards' SEAC, but later constructed the second ABNER and received a series of contracts for equipment using similar components. Technitrol went on to market a varied line of special and general-use equipment, much of it based on this experience. Another example is NSA's NOMAD contract with Raytheon Corporation. The NOMAD design was the direct forerunner of the Datamatic 1000, which was transformed into one of the early machines in the Honeywell line. realization, in 1955, that the transistor had a bright future as an electronic component, led to this Agency's sponsorship of the construction by Philco Corporation of NSA's first practical, transistorized computer, SOLO. Marketed commercially as the Transac S-1000, it became the world's first commercial transistorized computer. Beginning with the EDPM Type 701, the Agency-IBM experience is very impressive. Probably very few realize that IBM based much of its early computer philosophy upon NSA's experience with large data-processing problems. Certain features of the 704, representing improvements on the 701, resulted from suggestions by NSA personnel; similarly, the 702 was improved to become the 705. The PLAN-TATION (later RANCHO) study contract for HARVEST design, as well as NSA support for memory and magnetic tape researches, not only influenced IBM's 7030 (STRETCH) but also resulted in solving a number of fundamental logic and processing problems never before confronted in the computer field. Finally, the LIGHTNING researches into ultra-high-speed computer circuits and components -- work done under contract by IBM, Remington-Rand-UNIVAC, RCA, and others -- have undoubtedly had the greatest influence in the development of new computers and other digital equipment with basic operation times measured in nanoseconds (billionths of a second).

#### CHAPTER 2

#### AGENCY-SPONSORED COMPUTERS

In addition to operating an extensive computer installation, NSA has been a prime sponsor of computer developments. Of the nine electronic computer projects discussed in the following sections, two, ABNER and CUB, were designed and built by NSA (or predecessor) personnel. The rest were built under contract, following logical designs conceived or inspired by NSA personnel.

#### ATLAS I and ABEL

In the summer of 1946, Moore School of Electrical Engineering, University of Pennsylvania, sponsored a series of lectures on electronic computers. Among those who attended was LCDR James T. Pendergrass, a young mathematician at Navy's Communications Supplementary Activities, Washington (CSAW). As a result of hearing the computer proposals described at that time, LCDR Pendergrass prepared a report in which he proposed that the Navy acquire such a machine. His report included a general description of the proposed machine's logic, its code of instructions, and coded examples of typical problem solutions. The particular design advocated was of the class known as one-address logic, and was based on the I.A.S. Computer then being developed at the Institute for Advanced Study, Princeton, New Jersey. CSAW went ahead with plans for construction of ATLAS I, and CSAW personnel perfected most of the basic algorithms, or detailed machine logic for executing each instruction. The contractor, Engineering Research Associates of St. Paul, Minnesota, used MIT's WHIRLWIND I logical design to a great extent. ATLAS I was delivered on 8 December 1950 and was running before Christmas. It employed parallel circuitry, contained approximately 2700 tubes, and cost about \$950,000. Figures 3 and 4 show views of this machine.

Although the original proposal had specified that the ATLAS high-speed internal memory was to utilize Selectron tubes, a decision was made to substitute a 16,384-word magnetic drum of a type similar to one already placed in operation by E.R.A. in other special-purpose equipment built for the Navy. Also, whereas ICDR Pendergrass's proposal described a machine with 36-bit<sup>2</sup> words (each word containing two one-address instructions), the ATLAS I design was finally based upon 24-bit

3 de la companya del companya de la companya del companya de la co

100

Selectron was the specially-designed electrostatic storage tube under development by Jan Rajchman at RCA's Princeton Laboratories. The development never achieved sufficient reliability for use as a practical computer memory.

<sup>2 &</sup>quot;bit" -- binary digit

Figure 3 —ATLAS I Console

Figure 4-ATLAS I Main Frame, with Input Tape Reader in Foreground, Console in Background

words (each with one single-address instruction). memory was equipped with a flexible feature called "interlace," that permitted variations in address layout to be made for each program, using a plugboard setup. In effect, "lines" around the drum were renumbered by transposing certain bits of the address selection register in order to allow longer or shorter intervals between successive effective addresses, according to the particular needs of the program. Careful programming in conjunction with careful planning of the interlace plugging made it possible to attain extremely high speeds for given programs, compared to running time of programs written without attention to interlace. Thus, access time1 could be reduced to 32 microseconds under the best conditions, compared with an average of 8,500 microseconds or a maximum of 17,000 microseconds. In May 1951, a modification, the "skip" feature, was introduced that added flexibility to programming by allowing the program address counter to advance by intervals greater than one (9, 17, 33, or 65). In effect, the operation of the interlace feature was made partly automatic. In June 1951, the installation of a "dial interlace" feature made selection of the interlace plugging simpler and eliminated the necessity of actually changing plugboards. Other features of ATLAS I's original design included logical multiply instruction, vector addition, several forms of ordinary arithmetic instructions, conditional jump instructions, and an elementary input-output procedure using punched paper In 1952, an interesting new feature, the random jump instruction, was added. Employing a separate electronic attachment that supplied random bits of zero or one, this instruction made possible the generation of streams of random characters. The photoelectric tape-reading equipment delivered with ATLAS I was found to be quite slow (140 characters per second) compared with ATLAS I internal speeds; nor was it under program control. It was replaced by the newly developed Ferranti photoelectric tape reader that had a speed of 300 characters per second. Table 2 contains the ATLAS I instruction repertoire.

Shortly after the completion of the ATLAS I design in 1949, a decision was made to construct a relay analog of the equipment, to assist in training programmers and to "debug" its programs (at least logically) before it was delivered. ABEL (fig. 5) was designed and constructed by CSAW personnel in about four months. Logically it was identical to ATLAS I, but its memory drum capacity was 2,047 words instead of 16,384, and its relay circuitry made it several hundred times slower.

<sup>1</sup> access time -- time required to locate and read a word from memory into the arithmetic unit or vice-versa.

After an initial period of perfecting operational and maintenance techniques, ABEL proved to be quite reliable. It was used not only for programmer training but also for generating various statistical tables. Principally because of the great difference in capacity of the memories of ATLAS I and ABEL, the latter could not be effectively used to debug large-scale ATLAS programs. After ATLAS I began operating at CSAW, ABEL was dismantled and transferred, through the Office of Naval Research, to the Navy Logistics Project at the George Washington University where it went back into service. After operation on the Navy Logistics Project for a time, it was presented to the George Washington University School of Engineering. Finally, in 1963, GWU presented ABEL to the Albert Einstein High School in Silver Spring, Maryland. Here upon advice of Agency representatives, it was dismantled for the last time.

Several months before the delivery of ATLAS I, an order was placed with ERA for the construction of another almost identical machine; it was delivered in May 1953. In 1956, both machines were modified by the addition of high-speed core1 storage in the amount of 4,096 words. This addition modernized the machines and eased the programmers' burden; for before the addition of the high-speed magnetic-core memory, the extra effort required of programmers in putting instructions and constants in those locations in the memory best adapted to maximim use of the interlace feature was often excessive. In 1957, both ATLAS I's were moved to Fort Meade, and in November 1959 both machines were taken out of operation. ATLAS I, Serial 1, was salvaged, and the components used for other purposes; in March 1960, Serial 2 was shipped to the Anti-Submarine Research Center, SACLANT, NATO Forces, at La Spezia, Italy.

From a maintenance point of view, both machines performed extremely well. Although periods of down time for modifications and additions were necessary, the machines were usually operational above 90 percent in a reporting period. Many useful programs were written for ATLAS I, particularly for statistical and mathematical problems. Although the instructions were well-balanced for statistical and analytic uses, and the machines were designed and built for reliable operation, ATLAS I could not be used for problems demanding the handling of large volumes of data because of the lack of a magnetic-tape facility.

<sup>1</sup> core -- also, rings or toroids, of magnetic ferrite material, strung at the junctions of intercrossing wires. Each core represents one bit of storage capacity. Thus, a 1,024word memory of 24-bit words would take the form of a stack of 24 matrices, each matrix being a square array of cores, 32 cores to a side.

#### ATLAS II

The second secon

Several months before ATLAS I was delivered, a new task was established that provided for the design of a successor. ATLAS II and ATLAS I differed in the following respects:

- 1. Storage -- Whereas ATLAS I had only drum storage, ATLAS II had, in addition, high-speed electrostatic storage for 1,024 words.

- 2. Word Size -- The word size on ATLAS II was 36 bits. ATLAS I word size was only 24 bits.

- 3. Instruction Logic -- ATLAS II used two-address instruction logic; ATLAS I, one-address.

- 4. Order Code -- Instruction sophistication was increased on ATLAS II.

- 5. Input-output -- ATLAS II had program-controlled input-output instructions. A lack of this capability was a serious drawback for ATLAS I.

Two-address instruction logic was unique among computer projects. In some instructions, the two addresses specified the locations of two operands; in other instructions, one of the addresses was an operand and the other a destination location. Among the more sophisticated new instructions were the repeat instruction (see ABNER, page 14), several modular-arithmetic instructions, a scale factor instruction, and an index jump instruction.

ATLAS II was installed in October 1953. A second machine was also constructed, and it was delivered in December The second ATLAS II differed from the first only in that it had a high-speed ferrite-core memory rather than an electrostatic tube memory. Originally the plan was to equip ATLAS II with Raytheon magnetic-tape drives using a data representation of one character per frame. However, a change was made to a conservative scheme for data representation involving two positions per information bit, resulting in three tape frames per Subsequently, this latter representation was felt character. to be too inefficient for most large problems. With the objective of achieving tape interchangeability and speeding up magnetic-tape operations, a redesign effort was undertaken. However, this modification never reached operational effectiveness.

Even though somewhat handicapped by lack of an effective magnetic-tape system, both ATLAS II's contributed considerably to the solution of many problems. Reliability was high for both machines, but Serial 1 required somewhat more maintenance attention than Serial 2 because of the electrostatic tube storage. ATLAS I and ATLAS II were forerunners of the first two in a commercial line of Remington-Rand computers, the UNIVAC 1101 and 1103 respectively. Also, ATLAS II was the logical

model for the first transistorized computer, SOLO (described on page 29). ATLAS II, Serial 1, was taken out of operation in February 1960 and donated to the University of Texas; Serial 2 was turned over to the Second Army for disposal in May 1962. Figs. 6, 7, and 8 show three views of ATLAS II.

ABNER and BAKER

In December 1946, the first Pendergrass Report (see ATLAS I, page 8) was received at the Army Security Agency, one of NSA's predecessor agencies. The potential value of electronic computers in ASA applications was recognized immediately, and plans were made to consider the acquisition, by ASA, of a machine similar to Navy's proposed ATLAS. At that time, 1947, there were four main centers of electronic computer activity (see Table 3, page 97). During 1948, ASA analysts made visits to these installations, attended lectures at the Bureau of Standards' Digital Computer Laboratory, and performed programming experiments using ATLAS, UNIVAC, EDVAC, and RAYDAC order codes. The result of these investigations was a report favoring a design using four-address logic (RAYDAC or EDVAC) over the one-address logic (ATLAS or UNIVAC).

Four-address logic was favored for the following reasons:

- でもを見れていていたとうのできるとは、これのでは、これのでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本のでは、日本

- 1. Time estimates for executing representative operations showed higher speeds.

- 2. A philosophic conviction that the bulk of computer operations in ASA applications would be characterized by relatively simple operations on many data items rather than more complex operations upon data retained in the accumulator.

In addition, UNIVAC was rejected for Agency use because it used decimal arithmetic internally and could only manipulate data as alphanumeric characters. Because of the many examples of Agency processes using binary notation, a binary machine was felt to be a definite requirement.

Based on the foregoing report recommendation, attempts were made to get estimates and commitments for building such a machine. The Raytheon Corporation was already committed to complete a first machine for Navy's Bureau of Aeronautics, and would not promise delivery of a second machine in less than three years. Moore School had undertaken to build EDVAC for Army Ordnance and could not consider offers for a possible second machine. In May 1948, Reeves Instrument Corporation announced that it was entering the digital computer field with REEVAC, a proposed machine based on EDVAC design. The basic EDVAC logic provided for 45-bit words and a maximum of 16 four-

Figure 6.—ATLAS II Main Frame (Partial View)

Figure 7.—ATLAS II Console

Figure 8.—ATLAS II Input-Output

address instructions. Its 1024-word memory was to be composed of mercury delay lines, with minimum access time being 48 microseconds and actual access varying between 48 and 384 microseconds.

Dr. Samuel Lubkin, formerly at Moore School, headed the effort at Reeves. His proposed design contained several improvements upon the design of the EDVAC, and his price and promised date of delivery were attractive. But just as a contract with the Reeves Corporation was taking form, the company abandoned its plans to produce digital computers and released Dr. Lubkin to the staff of the National Bureau of Standards. Soon after, in August 1948, the Army Security Agency and the NBS concluded an agreement which provided that the Bureau would produce a design for a computer that ASA engineers would build. NBS simultaneously would be designing and building a similar computer for themselves -- one of more modest capabilities. Also, NBS was to place the order for the mercury delay line memories for both machines. Shortly thereafter, several meetings were held to settle on the functional design of the ASA machine, and, to orient ASA engineers in their early design efforts, NBS engineers gave a series of lectures on digital computer logic. The proposed ASA machine was called ABNER.

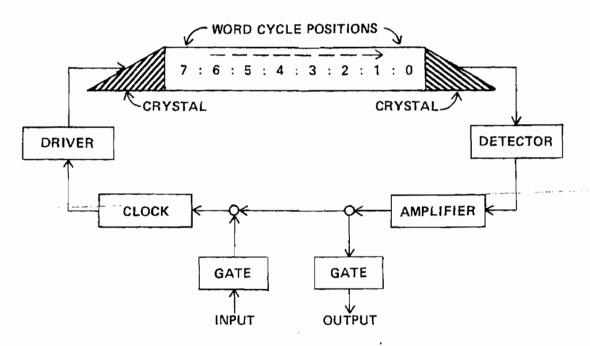

ABNER's mercury delay line memory was of particular interest. The acoustic delay line was developed around 1946 at the Moore School by Eckert, Sheppard, and Sharpless during planning for EDVAC. A succession of pulses (signal or no-signal) travels through an acoustic medium, say mercury, from one end to the other of a "delay line." Figure 9 shows a diagrammatic view of a mercury delay line. At the input end of the line is a crystal that converts an electrical pulse to a mechanical wave which travels through the mercury to the other end, where another crystal reconverts it to an electrical signal. The series of electrical signals is recirculated back to input, after passing through detector, amplifier, and driver circuits to restore the shape and strength of the pulses. Also, in the part of the cycle external to the delay line are input and output circuits and "clock" pulses for synchronization. cury, the pulses travel at the speed of sound, which is much slower than the speed of electrical signals, and thus the delay in going from one end of the line to the other constitutes a form of storage.

In ABNER, the mercury tank was a glass tube about two feet long; the delay time was 384 microseconds, or eight words of 48 bits1 at one-megacycle-per-second rate. Thus the 1,024

では、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmのでは、100mmので

The actual computer word length was 45 bits, allowing a 3-microsecond interval between words.

FIGURE 9. MERCURY DELAY LINE (DIAGRAMMATIC)

words were contained in two cabinets holding 64 mercury delay lines each. Figure 10 shows one side of one such cabinet, containing 32 tubes of mercury. (In the figure the actual glass tubes are not visible, being inside the metal cases shown in the upper part of the picture.)

Because of the great variation between minimum access time and the maximum, efforts were made to minimize such delays. Mention has been made above of the improvements possible in ATLAS using ingenuity together with the interlace feature, when special care was taken in placement of words on the drum (page 10). In the case of ABNER, the savings by careful programming was not as great, but worth the effort. Referring to the diagram of Figure 9, a word at cycle position 0 would be immediately available for readout (access time: 48 microseconds), while a word at cycle position 7 would take 8 x 48, or 384 microseconds to be read (or written into). Therefore, instruction words and operands would be carefully placed at memory locations that would be immediately available, if possible, bearing in mind cycle positions (the actual memory address modulo 8) and the known execution times of instructions.

For the next six or eight months, ASA engineers, working closely with several programmers, moved at full speed to perfect the engineering logic of the original set of instructions and devised several additional refinements. Also, primarily to acquire experience, they designed and built an input decimal-to-binary conversion device. About this time (July 1949) it became apparent to ASA that NBS would not be able to complete the design of ABNER in a reasonable time, principally because of pressure to expedite completion of their own machine, SEAC. So the decision was made to go ahead and build ABNER without waiting for NBS. ASA engineers estimated that they could build the machine in two years.

Meanwhile, the programmers, who had made programming experiments using the several available computer designs, became convinced that Agency operations justified flexibilities in data manipulation not available in these designs or in ABNER as it was conceived at the time. They began work on a set of special computer instructions to be considered for inclusion in a future improved computer. Three principal classes of operations required special attention: character transformations, data-stream manipulations, and paired stream comparisons. These three lines of attention became interrelated and produced a combined solution that is quite interesting and historically significant. This result was possible because of the intimate working relationship between the programmers and engineers.

Figure 10 -- ABNER Serial 1 Memory Cabinet

Bearing Marie William

These new features were incorporated in the machine under construction rather than waiting for a successor computer. The following describes briefly how the three requirements were implemented:

- 1. Character transformations were treated in the computer as modular addition; that is, the corresponding alphanumeric characters of two words are summed, modulo n, where the value of n varies from 2 to 32. For situations dealing with character sets containing more than 32 characters, two additional instructions were devised: one that dealt with two streams of 10-bit characters (four in each word), and another in which the pairs of characters to be acted upon were within the same word.

- Data stream manipulations originated as a requirement to transfer .groups of words among different portions of internal memory. The first version was thus a block transfer of a fixed number of words and was based upon a modification of the Shiftand-Extract instruction so as to repeat the instruction a fixed number of times. The capability of executing such an instruction any number of times came about with the development of the Halt feature. feature originally was visualized as a means of automatically monitoring computer instruction executions so as to signal the completion of a specific routine. Using the Halt instruction to signal the completion of the final execution of a repeating instruction and extending the repetition feature to apply to most ABNER instructions made these two features -- Halt and Repetition -- completely general and yielded a flexible basis for manipulating streams of data.

- Paired stream comparison was specified by the programmers as deserving special consideration because of the relative inefficiency of standard computer techniques for performing character-by-character comparison operations. The engineers outdid themselves in satisfying this particular requirement, and the resulting instruction was undoubtedly the most sophisticated ever proposed for a general-purpose computer. Nicknamed "Swish" to depict its action, this instruction accomplished the logical equivalent of a complete, high-speed comparator. In effect, it (a) passed two streams of five-bit characters from memory through an analytic unit, (b) compared groups of characters (group size between 1 and 63 characters) for coincidence, (c) counted the number of group coincidences, (d) stored the coincidence count in a memory location specified

in the same instruction, and (e) restored one of the streams to memory at a specified offset from its original place in memory (offset between zero and eight characters). One significant result of experience with ABNER and the Swish instruction has been its influence on the design of the Streaming units of HARVEST.

When planning ABNER's input-output features, the designers placed great emphasis on achieving flexibility, sometimes at the expense of speed. The result was an input-output capability more complete and varied than that of any computer commercially available at the time. This included:

- 1. Up to six magnetic tape drives -- These could be operated for reading or writing in both directions, with words read into or out of memory in ascending or decending order or not in consecutive order at all. Block size was eight words. Tapes were operable either under computer control or off-line for conversion from or to other media.

- 2. Punched paper-tape reader and punch -- A CXCO<sup>1</sup> electric typewriter with a tape reader and punch was first used; later the tape reader was replaced by a Ferranti photoelectric reader with a much greater speed (300 characters per second).

- 3. Punched-card reader and punch -- An IBM collator for reading punched cards and a modified card punch were operable either under computer control or off-line using the converting unit.

- 4. Converting unit -- This unit was designed to accomplish data conversion between almost any two media, including punched paper tape, punched cards, magnetic tape, and ABNER storage. It included a plugboard for performing simple character-for-character substitution upon input or output. Its principal utility in practice was as an off-line converter between magnetic tape and other media.

- 5. Input/output typewriter -- Direction of insertion of characters into memory words could be chosen, and substitution plugging on output characters was available.

- 6. Console -- Although physically very small (12x14x10 inches), the console provided great flexibility for manually communicating with the computer and its various

Alan.

A A STATE

1

A Navy-sponsored development, manufactured by Commercial Controls Corporation

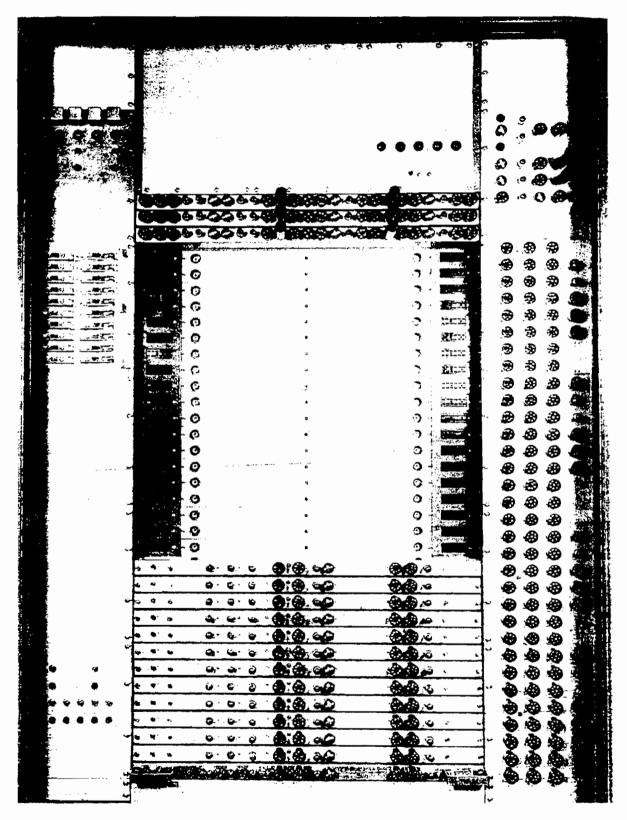

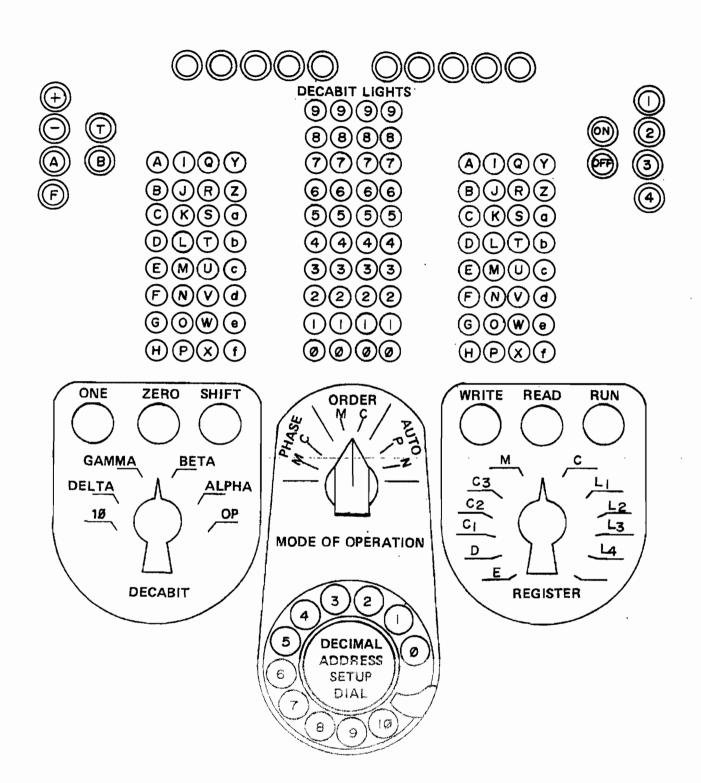

registers. Also, a novel feature was its built-in binary-to-decimal and decimal-to-binary conversion equipment for dealing with memory addresses in either decimal or binary form. An array of lights indicated the status of machine operations and the causes of machine stops. Figure 11 is a drawing of the console controls, only slightly smaller than actual size.

Because the Agency had no prior experience in digital computer design and construction — indeed, no computers of this magnitude and speed range had yet been completed by anyone — ASA engineers faced a number of difficult problems. The mercury delay line memory was obtained from the Technitrol Company, and magnetic tape drives were purchased from the Raytheon Manufacturing Company. All other components were ordered from vendors or fabricated in the Agency. For example, one extremely critical item, electric delay lines, had to be designed and fabricated by ASA engineers and technicians. The power supplies, console, and input-output facilities were also troublesome items, primarily because initially they had less reliability than most parts of the computer.

By September 1951, ABNER was completed, and the checking out of individual features got under way. This turned out to be a very complex process, partly because of inadequate instrumentation and also because of the tremendous number of variations and instruction combinations possible. In April 1952, the last analytic instruction was checked out. The complete list of ABNER instructions is reproduced in Table 4.

In April 1955, a second ABNER was delivered, constructed under contract by Technitrol Engineering Corporation. Logically it was a copy of ABNER, Serial 1, but it used quartz instead of mercury in the memory's delay lines. An additional innovation was the inclusion of 128 words of rapid access, or "scat," memory, as well as 1024 additional words of main memory. Its engineering and layout were considerably better, and the design of its console was entirely different. A latemodel Remington-Rand line printer was installed later. Much debugging was necessary before the system became reliable, so it had not given much operational service when, in 1958, it was moved to Fort Meade. In January 1960 ABNER, Serial 2 was retired from active service. (ABNER, Serial 1, was dismantled and disposed of when the move to Fort Meade took place.) Figures 12, 13, and 14 show three views of the second ABNER.

Compared with ATLAS I, neither model of ABNER had high operational reliability, although they had a number of periods of good "up-time." The use of dynamic serial circuitry in ABNER and a large concentration of complex analytic instruc-

FIGURE 11. ABNER (1) CONSOLE PANEL

Figure 12.—ABNER Serial 2 Console

Figure 13.-ABNER Serial 2, Raytheon Tape Drives

Figure 14.—ABNER Serial 2 Main Frame

tions combined to make this machine extremely difficult to maintain. For example, the control of temperature of the quartz delay lines in the memory was always extremely critical, and the instruments used for measurement and regulation were inadequate. Also, the input-output equipment (IBM collator, Remington-Rand printer, electric typewriter, and Raytheon magnetic tape drives) were often out of operation; and computation was ineffective or erroneous when input-output errors arose.

However, ABNER design and construction laid the foundation for many important later developments. ABNER was among the first computers in the country to operate successfully magnetic tapes simultaneously with internal computation. Its analytic instructions and other unique features made it possible to perform many specialized Agency data manipulations more efficiently than certain other computers having inherently higher speed circuitry. For the same reasons it was quite popular with programmers. Its "Swish" instruction was a model for several special-purpose machines, and was a forerunner of the HARVEST Streaming units. Many programs made good use of the magnetic-tape capabilities, as well as the analytic instructions.

ABNER, Serial 1, cost approximately \$600,000. It contained 1,500 tubes and 25,000 diodes. ABNER, Serial 2 cost about \$750,000.

In the fall of 1950, a proposal was made to build a slow-speed analog of ABNER, based on experience in building ABEL, the analog of ATLAS I. Although there was some opposition to this proposal because of ABNER's complexity, the group of engineers who had built ABEL was assigned the task. The new analog was called BAKER and was built using electric relays and a magnetic drum memory.

Although ABNER was designed to use serial circuitry entirely — in fact, many of its unique analytic features were possible because of that — BAKER engineers went ahead with the logical design and construction of BAKER using parallel circuitry, and succeeded in simulating the complete ABNER order code. The job took about two years; and, in September 1952, BAKER was tested. It was equipped with a slow-speed punched tape reader for input, and an electric typewriter and tape punch for output. Eventually all the logic was checked out, but the machine never operated reliably enough to be of much practical assistance in either training programmers or debugging ABNER programs. As a demonstration of a difficult engineering design job, the completion of BAKER was a remarkable achievement. The use of parallel

relay circuitry to simulate a complex electronic serial computer, however, should probably not have been attempted. Figure 15 is a view of BAKER.

NOMAD

Even before NSA's first electronic computer had been placed in operation (1950), Agency analysts recognized that certain priority problems would require special features in computers to manipulate large volumes of data. Planners of ABNER had made provisions for the inclusion of several Raytheon magnetic tape drives, and the UNIVAC system being built for the Bureau of the Census also placed emphasis on manipulations and statistical operations upon large volumes of data. However, it was evident that many jobs demanded far greater capability than could be expected of commercially available magnetic tape systems. In 1949, a study contract was awarded to Engineering Research Associates that resulted in a proposal called NOMAD1, providing for special-purpose sorting and datamanipulation facilities. The proposal to initiate a project for the development and construction of an equipment system of this nature was approved in 1950. Several companies were invited to submit proposals in response to the Purchase De-In September 1951, the Raytheon Corporation was scription. awarded a letter contract under which work was initiated. A definitive contract for the NOMAD system was executed in May 1952, on a cost-plus-fixed-fee basis. Although not the lowest bid, Raytheon's proposal was chosen because it demonstrated what seemed to be the best understanding of the problem to be solved, and its design presented a well-thought-out solution.

Raytheon's NOMAD proposal provided for an internal memory having two speed ranges, and arithmetic and control units of more or less conventional logic. In addition, a high-speed large capacity magnetic-tape system called "primary internal tape storage (PITS) was proposed, to be operated in conjunction with several sections of buffer storage. The PITS constituted the principal medium for the large volume manipulations called for by the purchase description and necessary for special developmental work on tapes, tape drives, and tape control systems.

Almost at the outset, Raytheon began investigations of alternative solutions to many technical questions before settling down to system design. The following is a partial list:

1. Memory -- The original proposal specified mercury delay lines. Magnetic cores later appeared as an attractive alternative. But whether to use metallic or ferrite cores was not settled for quite some time.

2. Instruction Logic -- The original Purchase De-

After "nomad," a wanderer, because sorted data have no fixed addresses.

scription called for one-address instruction logic, but results of an Agency-directed study indicated that three-address instructions were preferable.

- 3. Circuitry -- Pulse position modulation (PPM) gave promise of greater reliability than conventional pulse amplitude modulation and was considered for a time; however, after much testing, it was rejected.

- 4. Checking -- Raytheon engineers made elaborate plans for including checking and error-correcting circuitry. However, Agency management directed a minimization of such checking features because of the high cost of the large number of additional components.

- 5. PITS -- This large-volume magnetic tape system posed a number of problems -- tape handling, head design, tape manufacture, control logic, buffering, and the like. There was insufficient assurance that all these problems could eventually be solved.

In addition to technical problems, serious personnel and security dilemmas arose to plague the project. As early as February 1953, one of the company's key experts on tape systems resigned; later, the project manager himself failed to obtain full clearance, which made it difficult to explain problem background for certain of the system features. Finally, an evaluation of the contractor's effort, in 1954, concluded with a recommendation that the contract be terminated because of prohibitive time and cost overruns as well as the likelihood that NOMAD would be obsolescent at time of delivery. When the books were closed, the contract was shown to have cost the government approximately \$3,250,000.

Allowing the record to indicate that this expensive failure was due to contractor shortcomings might be more comforting, but an honest assessment of the NOMAD experience indicates that Agency actions or weaknesses may have been partly to blame. Among these are the following, cited as possible object lessons:

- 1. The construction contract was awarded before enough attention was devoted to design optimization.

- 2. Insufficient investigation was made of potential contractors' abilities to perform.

- 3. The Agency technical staff was too small to properly supervise the contract.

50L0

By January 1955, the substitution of the transistor for the vacuum tube in switching and power applications became so

widespread that the Agency created a new task, PEANUT, devoted to accumulating circuit information and to forming the basis for training other engineers in transistor technology. Later that same month, a proposal was made that the Agency sponsor the construction of SOLO, probably the country's first transistorized, large-scale, electronic digital computer -- a desksized, logical copy of ATLAS II. The proposal received the full support of the Director, who directed that the goal of this development was to be the construction of forty machines for decentralized operation in analytic areas. The contract to design and construct SOLO was awarded, in June 1955, to the Philco Corporation, then the only producer of high-speed transistors. A primary objective was to demonstrate the feasibility and reliability of transistors in computer circuits in a large computer system, using direct-coupled transistor logic. Later, subcontracts for the construction of the core memory and the power supplies were awarded to Remington-Rand-UNIVAC and Magnetic Controls Corporation, respectively.

Although SOLO was planned as a logical copy, it did differ from ATLAS II. Whereas ATLAS II had a drum memory of 16,384 words in addition to its high-speed memory, SOLO's internal memory was confined to 4,096 words of magnetic core storage. Also, since the smaller memory required only 12 bits, instead of 15, to address any word, the three extra bits were used as address modifiers to designate 12-bit portions of an operand word. This feature added flexibility and increased capacity for certain types of operations. In addition, SOLO had a new instruction, Expand Transfer, that facilitated the expansion of data packed "n" characters per word into a series of "n" words, one character each. Also, input to SOLO was by a Teletype high-speed punched paper-tape reader, operating at 100 characters per second; output was by a Teletype paper-tape punch or a Flexowriter at 10 characters per second.

The contractor's construction effort was slowed by a number of difficulties which could be attributed partly to the unsatisfactory power supplies initially delivered by one of the subcontractors, and partly to the instability of certain components of the other subcontractor's memory. After several time and cost overruns, the system was delivered in March 1958; it cost the government \$1,007,700. Principally because of the technical shortcomings just mentioned, NSA engineers spent approximately a year debugging the equipment. Power supplies were replaced, and the tape punch and Flexowriter were repaired.

SOLO was composed of a computer console and an inputoutput console (fig. 16) and contained 8,000 transistors, 3,700 resistors, 200 capacitors, and 8 vacuum tubes.

In spite of the difficulties, SOLO finally operated very reliably, but original ideas about its use were modi-Instead of many copies being made for operational use, only one SOLO was built, and its use limited to research. For example, it was used as the vehicle for testing and modifying the RCA magnetic tape drives under development for R/D. These three RCA magnetic tape transports had special features to provide flexibilities not available in commercial systems. Of course, this had the effect of extending SOLO storage capacity so that large experimental programs could be run. Also, a Potter tape transport was added to increase SOLO's inputoutput speed. Making these modifications locally, attendant Supervision, repairing, and debugging occupied some 35,000 man-hours, spread over several years. Although much effort and time were devoted to the project to attach and test the RCA tape drives, they never became operational because of difficulties and inconveniences in converting from primary input media. However, the Potter drive was quite effective because its tapes were interchangeable with those made on IBM Type 727 tape drives.

Operationally, SOLO programs were written for two purposes: (1) to produce empirical statistics in many problem situations preceding special-purpose equipment design, and (2) to simulate special-purpose equipment during design and construction. SOLO was the first computer extensively used by Agency engineers to assist in engineering logic-check or design optimization.

The original objective of SOLO -- to prove that a reliable operational computer could be constructed using direct-coupled transistor logic -- was attained. In August 1963, SOLO was removed from regular operation and turned over to a machine-processing group for training purposes.

#### BOGART

In Chapter 1, page 4, the problems attending the preparation of input data for computer treatment have been touched on. The difficulties inherent in Agency activities --lack of control of source material, variations in communications practices, rigid formatting requirements of computer programs -- had resulted in the construction of many different types of conversion equipment. In 1952 and 1953, suggestions were made for using especially designed digital computers for data conversion and editing and to "clean up" raw data for input to

Figure 16-SOLO

larger computers. During the NOMAD development, for example, one proposal for the solution of its anticipated massive data preparation, conversion, and formatting requirements was to build an additional computer for these purposes.

In December 1953, a proposal for the design and construction of such an "editing" computer was approved. The purchase description of BOGART specified a logical design based upon 7-bit words and provided for magnetic core and magnetic drum storage, punched paper-tape input, punched paper-tape and card output, and a flexible set of 3-word instructions. In July 1954, Engineering Research Associates Division of Remington-Rand was awarded a contract to build two of these machines. The decision was made to use diode and magnetic core logic for arithmetic and control circuitry; the basic memory cycle time was to be 20 microseconds.

Several months of programming experimentation showed that the small, 7-bit word size and the awkwardness of handling a 3-word group for every instruction caused much difficulty for programmers and put a strain on the memory capacity. In July 1955, a modification was made that provided for several index registers and larger word size (24 bits), with flexibility in dealing with 9-bit portions of any word. Now, also, four machines instead of two were to be constructed and equipped with IBM Type 727 magnetic-tape drives. Serial 1 was delivered in July 1957; Serials 2 and 3, in November 1957; and Serial 4 in January 1958. Subsequently, the pilot model was utilized as the central computer for the remote-operated system ROB ROY, so that five BOGART machines in all were delivered to the Agency.

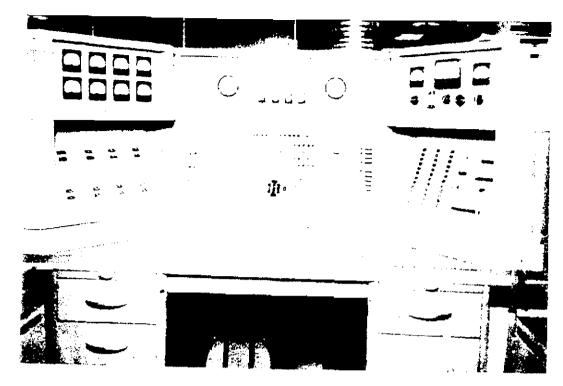

BOGART has operated extremely reliably. It has been in great demand for many jobs other than purely editing and data conversion. In 1957, an assembly program, SLAVE, was created, and in 1959 BARN OWL, an executive routine, was introduced. Later, BARN OWL was refined and expanded to include some compiling functions. As an operating system it became known as PHOENIX. The BBC Compiler, based on the ABC Compiler for the IBM 704, is also available. Figure 17 is a view of the BOGART console, and figure 18 is a view of BOGART Serial 2.

the second second second second second

After John B. Bogart, famous city editor of the New York Sun.

Figure 17 -- BOGART Console, with TBM 727 Tape Drives

figure 18 -- BOGART, Serial 2

In March 1960, in connection with an R/D task for the development of 2.5-megacycle, miniature, building-block circuit cards for electronic equipment construction, the decision was made to design and construct a small test vehicle. Shortly thereafter, the decision was changed to a full-scale digital computer for this purpose; and construction of CUB (figure 19) began in June 1960. An engineering and design lab within R/D designed and constructed the entire machine, and it was completed in January 1961.

The CUB computer was a small, general-purpose machine of limited processing capability. It contained approximately 1,000 printed circuit cards and was operable at normal room temperatures, using blowers for air circulation. The CUB word-size was only 12 bits, and each of its 32 instructions consisted of two words. Its memory capacity was 4,096 words; its cycle time, 8 microseconds. The typical, flexible one-address repertoire of instructions included a Repeat instruction similar to that in ATLAS II.

CUB was originally equipped with a photoelectric paper-tape reader (200 characters per second), and a Flexowriter paper-tape read/punch typewriter (10 characters per second). Later, to test the use of cards in control units for peripheral equipments, an Anelex high-speed printer and two IBM Type 7330 magnetic-tape drives were added. These-machines were then made available for use with other Agency analytic equipment. CUB was used to establish system design parameters and to assist logic designers of other machines in processing logic equations.

Despite its limited purpose and short construction time, CUB performed quite reliably and was very useful. With ABNER, it was one of the two general-purpose electronic digital computers totally constructed by Agency personnel.

UNIVAC 1224A (CRISPI)

UNIVAC 1224A is a name applied by the Sperry Rand Corporation to the computer that the company built for CRISPI, a bauded-signal receiving and processing system being developed by an R/D engineering and design group.

The UNIVAC 1224A is the heart of CRISPI, and its organization and instruction repertoire are directed toward the concurrent manipulation of 16 or more independent data-streams.

Figure 19.—CUB

Figure 20.—Partial View of CRISPI, Showing Paper-Tape Input, UNIVAC 1224A, and "B" Console

Features descriptive of the UNIVAC 1224A are:

Word length: 24 bits plus 2 parity bits

Memory size: 16,384 words

Memory cycle time: 4 microseconds

Number of instructions: 28 single-address

Number of index registers: 31 (one live, others

in memory)

Input: up to 16 independent data-streams

Output: variety of outputs (hereafter described)

Number of circuit cards: approximately 1000

Physical dimensions: 24" wide, 27" deep, 72" high

Power requirement: approximately 1000 watts

Specifications: designed to meet MIL-E-16400

Mean time between failures: 1,200 hours (estimated)

The logic of the input/output portion of the UNIVAC 1224A provides for communication with several external devices. To prevent simultaneous access to memory by more than one external device, a priority system regulates accesses by prorating them fairly. Present external devices include papertape input/output device, printing facility, magnetic-tape unit, on-line communication line, and one to four operator consoles. The paper-tape input/output device provides a minimal capability and consists of a 300-frames-per-second photoelectric reader and a 110-frames-per-second paper-tape punch.

The printing facility uses a one-way-only flow of data and can be any device that will match the computer's electrical and logic interfaces. The device presently used is a printer control unit designed to distribute up to 64 output streams to paper-tape punches on one-at-a-time page printers.

A bidirectional interface on the magnetic-tape facility permits data to be transferred from computer to tape or from tape to computer but not concurrently. The magnetic-tape control unit is designed to handle up to four transports. The tape format is compatible with IBM Type 729 low-density tapes.

The on-line input/output facility permits bidirectional data exchange between two computers or between one computer and some other asynchronous device such as a communication center.

The operator console is the critical, on-line interface equipment between the signal tuning equipment (receivers, demodulators, and the like) and the computer. The console allows the operator to control the flow of data to the computer and to monitor the activity in the computer. The logic interface between the console and the computer is such that a variety of operator consoles may be used. To date, four different consoles have been conceived, two of which have been constructed.

Two UNIVAC 1224A computers have been put into use, the first in June 1963 and the second in July 1963. Performance has been excellent. Four more are under construction for delivery early in 1964. Procurement of 10 more for other purposes is being initiated. Figure 20, a partial view of CRISPI, shows the punched paper-tape input unit, the UNIVAC 1224A computer, and the operator console, type B.

#### HARVEST

The most important characteristic of the stored-program general-purpose, electronic digital computers has been their spectacular versatility -- their general usability for statistical jobs, logical jobs, analytic jobs, and the like. ever, because of the elementary nature of most individual computer operations, this characteristic is often a disadvantage for performing certain specialized operations. In other words, a special-purpose machine can be built with analytic power superior to any general-purpose system, assuming equal states of the engineering art. On the other hand, this superior power has not come easily. Special equipments have well-known disadvantages -- initial delay for specification, design, and construction; possible disappearance of problem requirement; and high cost per machine. Special efforts were made to reduce these disadvantages, to cut down costs and delivery time. In April 1954, a possible solution of this machine designer's dilemma was proposed in FARMER, a system of general-purpose and special-purpose equipment that would include suitable provisions for switching, a control, and data transmission. FARMER would attempt to combine the advantages of both types of equipments, minimizing or eliminating the disadvantages of both, by providing (1) a powerful, general-purpose computer capable of controlling the operation of special-purpose attachments as well as the flow of data through the system, and (2) specialpurpose, high-speed attachments, built and connected as problem requirements dictated. Thus, storage, input-output, and statistical requirements of special problems could be standardized and provided in the general-purpose portion, leaving only the heart of a proposed special analytic attack to be designed and constructed.

Just about the time that FARMER was being considered, the Agency's efforts to get the large-scale computer system, NOMAD, were reaching a crisis (see page 28, 29). The contract with Raytheon Manufacturing Company was terminated in June 1954. During that same month, an Agency committee assigned to set priorities in equipment planning took up consideration of the FARMER proposal. With current NOMAD difficulties an important factor in its discussions, this committee created an ad hoc study group for the purpose of surveying the Agency's

needs for large-scale analytic equipment and preparing recommendations for design studies. The report of this group, published in November 1954, approved the FARMER proposals and emphasized the following particularly desirable characteristics for the proposed system and its parts:

1. Compatibility and uniformity.

2. An increase in speed as far as practicable.

- 3. Break-up into separate units that can be freely interconnected.

- 4. Multiple copies of those units that are required most frequently.

- 5. Ability to put early units into operation before other FARMER units are completed.

- 6. Ability to incorporate new unit-types as their need appears.

During the next few months, some effort was made to begin launching a FARMER System. Detailed investigations were conducted to determine what special attachments should be considered, and some high-speed circuitry research was undertaken; but little of a concrete nature really got under way.

In May, and again in August 1955, IBM representatives contacted the Agency and described their STRETCH program of engineering and logic researches — researches directed towards development of an advanced computing system having one hundred to two hundred times the power of the best existing machine. These prospective features were based on the following specific developments:

1. Transistor fabrication and circuitry advances in the 10-megacycle-per-second range.

2. Advanced core-memory techniques showing promise of reaching access times of about one-half microsecond for small memories (about 1,000 words) and two microseconds for larger memories (approx. 16,000 words).

- 3. Improvements in magnetic-tape handling systems, making the attainment of an information transfer rate of upwards of 1,200,000 bits per second appear practicable.

- 4. Revolutionary logical design and organization improvements -- program look-ahead, automatic indexing, automatic table lookup, and the like.

IBM representatives explained that the company had invested many millions in the research program but was now too short of funds to build a hardward system to test the logic, circuitry, and components. Because of NSA's need for such a

large-scale system and because of this Agency's ability to test-operate the system, IBM proposed that the first STRETCH system be built and delivered for a fixed price of \$3,500,000.

Although Agency technical personnel considered this a great bargain, it was rejected because our engineers were not convinced that the high-speed memory techniques were developed and proven ready to incorporate into a hardware system, and also because Agency requirements for a system of this magnitude justified a special effort to insure that its design was more Agency-oriented. The strong recommendation of the Agency engineers and analysts involved was that these developments should somehow be incorporated into the planned FARMER system. For this reason, after Agency discussion and negotiation with IBM, two 18-month study contracts, SILO and PLANTATION, were awarded to IBM.